- 您现在的位置:买卖IC网 > PDF目录1891 > AD7142ACPZ-500RL7 (Analog Devices Inc)IC CAP-TO-DGTL CONV PROG 32LFCSP PDF资料下载

参数资料

| 型号: | AD7142ACPZ-500RL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 28/73页 |

| 文件大小: | 0K |

| 描述: | IC CAP-TO-DGTL CONV PROG 32LFCSP |

| 标准包装: | 1 |

| 类型: | 电容数字转换器 |

| 分辨率(位): | 16 b |

| 采样率(每秒): | 250k |

| 数据接口: | 串行 |

| 电压电源: | 单电源 |

| 电源电压: | 2.6 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 标准包装 |

| 其它名称: | AD7142ACPZ-500RL7DKR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页

AD7142

Rev. A | Page 33 of 72

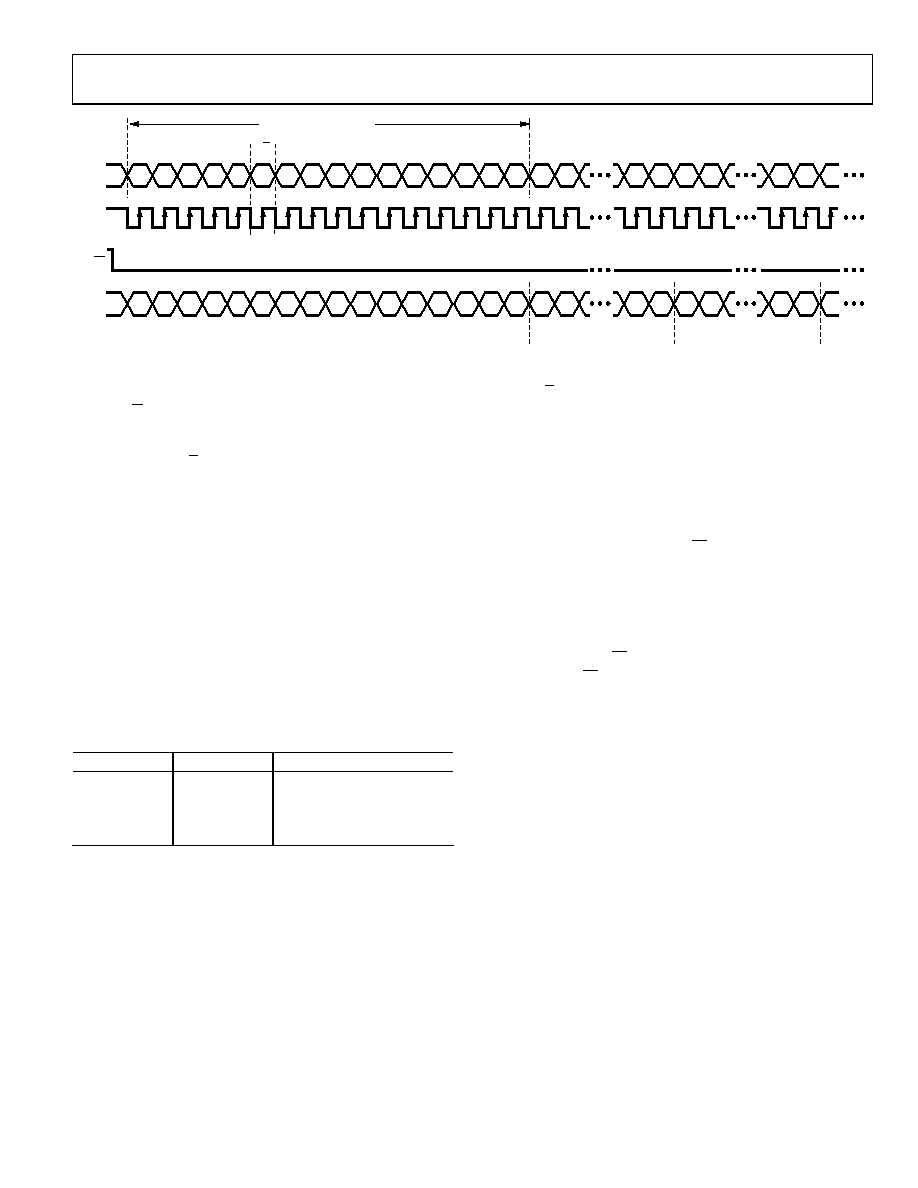

05702-

036

SDI

CW

15

CW

14

CW

13

CW

8

CW

1

CW

0

XX

SCLK

CW

12

XX

X

READBACK DATA FOR

STARTING REGISTER ADDRESS

X

1

32

2

3

4

1516

1718

31

34

33

48

47

49

CS

CW

11

CW

10

CW

9

CW

7

CW

2

CW

6

CW

5

CW

4

CW

3

11

12

13

14

56

78

910

XXX XXX XXX

XXX D15 D14

D1

D0

D1

D0

D15

D14

XXX XXX XXX XXX XXX XXX XXX XXX XXX XXX XXX XXX

SDO

16-BIT COMMAND WORD

ENABLE WORD

R/W

REGISTER ADDRESS

NOTES

1. MULTIPLE REGISTERS CAN BE READ BACK CONTINUOUSLY.

2. THE 16-BIT CONTROL WORD MUST BE WRITTEN ON SDI: 5 BITS FOR ENABLE WORD, 1 BIT FOR R/W, AND 10 BITS FOR REGISTER ADDRESS.

3. THE ADDRESS AUTOMATICALLY INCREMENTS WITH EACH 16-BIT DATA-WORD BEING READ BACK ON THE SDO PIN.

4. CS IS HELD LOW UNTIL ALL REGISTER BITS HAVE BEEN READ BACK.

5. X DENOTES DON’T CARE.

6. XXX DENOTES HIGH IMPEDANCE THREE-STATE OUTPUT.

7. 16-BIT COMMAND WORD SETTINGS FOR SEQUENTIAL READBACK OPERATION:

CW[15:11] = 11100 (ENABLE WORD)

CW[10] = 1 (R/W)

CW[9:0] = [AD9, AD8, AD7, AD6, AD5, AD4, AD3, AD2, AD1, AD0] (STARTING MSB JUSTIFIED REGISTER ADDRESS)

READBACK DATA FOR

NEXT REGISTER ADDRESS

Figure 49. Sequential Register Read back SPI Timing

I2C COMPATIBLE INTERFACE

The AD7142-1 supports the industry standard 2-wire I2C serial

interface protocol. The two wires associated with the I2C timing are

the SCLK and the SDA inputs. The SDA is an I/O pin that allows

both register write and register readback operations. The AD7142-1

is always a slave device on the I2C serial interface bus.

It has a 7-bit device address, Address 0101 1XX. The lower two

bits are set by tying the ADD0 and ADD1 pins high or low. The

AD7142-1 responds when the master device sends its device

address over the bus. The AD7142-1 cannot initiate data

transfers on the bus.

Table 17. AD7142-1 I2C Device Address

ADD1

ADD0

I2C Address

0

0101 100

0

1

0101 101

1

0

0101 110

1

0101 111

Data Transfer

Data is transferred over the I2C serial interface in 8-bit bytes.

The master initiates a data transfer by establishing a start con-

dition, defined as a high-to-low transition on the serial data

line, SDA, when the serial clock line, SCLK, remains high. This

indicates that an address/data stream follows.

All slave peripherals connected to the serial bus respond to the

start condition and shift in the next eight bits, consisting of a

7-bit address (MSB first) plus a R/W bit that determines the

direction of the data transfer. The peripheral whose address

corresponds to the transmitted address responds by pulling the

data line low during the ninth clock pulse. This is known as the

acknowledge bit. All other devices on the bus now remain idle

when the selected device waits for data to be read from, or

written to it. If the R/W bit is a 0, the master writes to the slave

device. If the R/W bit is a 1, the master reads from the slave device.

Data is sent over the serial bus in a sequence of nine clock

pulses, eight bits of data followed by an acknowledge bit from

the slave device. Transitions on the data line must occur during

the low period of the clock signal and remain stable during the

high period, since a low-to-high transition when the clock is

high can be interpreted as a stop signal. The number of data

bytes transmitted over the serial bus in a single read or write

operation is limited only by what the master and slave devices

can handle.

When all data bytes are read or written, a stop condition is

established. A stop condition is defined by a low-to-high

transition on SDA when SCLK remains high. If the AD7142

encounters a stop condition, it returns to its idle condition, and

the address pointer register resets to Address 0x00.

相关PDF资料 |

PDF描述 |

|---|---|

| AD7143ACPZ-1REEL | IC CONV CAP-TO-DGTL PROG 16LFCSP |

| AD7147A-1ACBZ500R7 | IC CDC 13CH I2C W/RAM 25WLCSP |

| AD7147WPACPZ-1500R | IC CAP-TO-DGTL CONV PROG 24LFCSP |

| AD7150BRMZ-REEL | IC CAP CONV 2CH ULT LP 10MSOP |

| AD7151BRMZ-REEL | IC CAP CONV 1CH ULT LP 10MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7142ACPZ-500RL71 | 制造商:AD 制造商全称:Analog Devices 功能描述:Programmable Controller for Capacitance Touch Sensors |

| AD7142ACPZ-REEL | 功能描述:IC CAP-TO-DGTL CONV PROG 32LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - ADCs/DAC - 专用型 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:50 系列:- 类型:数据采集系统(DAS) 分辨率(位):16 b 采样率(每秒):21.94k 数据接口:MICROWIRE?,QSPI?,串行,SPI? 电压电源:模拟和数字 电源电压:1.8 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(6x6) 包装:托盘 |

| AD7142ACPZ-REEL1 | 制造商:AD 制造商全称:Analog Devices 功能描述:Programmable Controller for Capacitance Touch Sensors |

| AD7143 | 制造商:AD 制造商全称:Analog Devices 功能描述:Programmable Controller for Capacitance Touch Sensors |

| AD7143ACPZ | 制造商:Analog Devices 功能描述:IC CDC 16BIT SMD LFCSP-16 7143 制造商:Analog Devices 功能描述:IC, CDC, 16BIT, SMD, LFCSP-16, 7143 |

发布紧急采购,3分钟左右您将得到回复。