- 您现在的位置:买卖IC网 > PDF目录10973 > AD723ARUZ (Analog Devices Inc)IC ENCODER RGB-NTSC/PAL 28-TSSOP PDF资料下载

参数资料

| 型号: | AD723ARUZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 3/20页 |

| 文件大小: | 0K |

| 描述: | IC ENCODER RGB-NTSC/PAL 28-TSSOP |

| 标准包装: | 50 |

| 类型: | 视频编码器 |

| 应用: | 照相机,互联网设备,机顶盒 |

| 电压 - 电源,数字: | 2.7 V ~ 5.5 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 28-TSSOP |

| 包装: | 管件 |

| 产品目录页面: | 788 (CN2011-ZH PDF) |

REV. 0

AD723

–11–

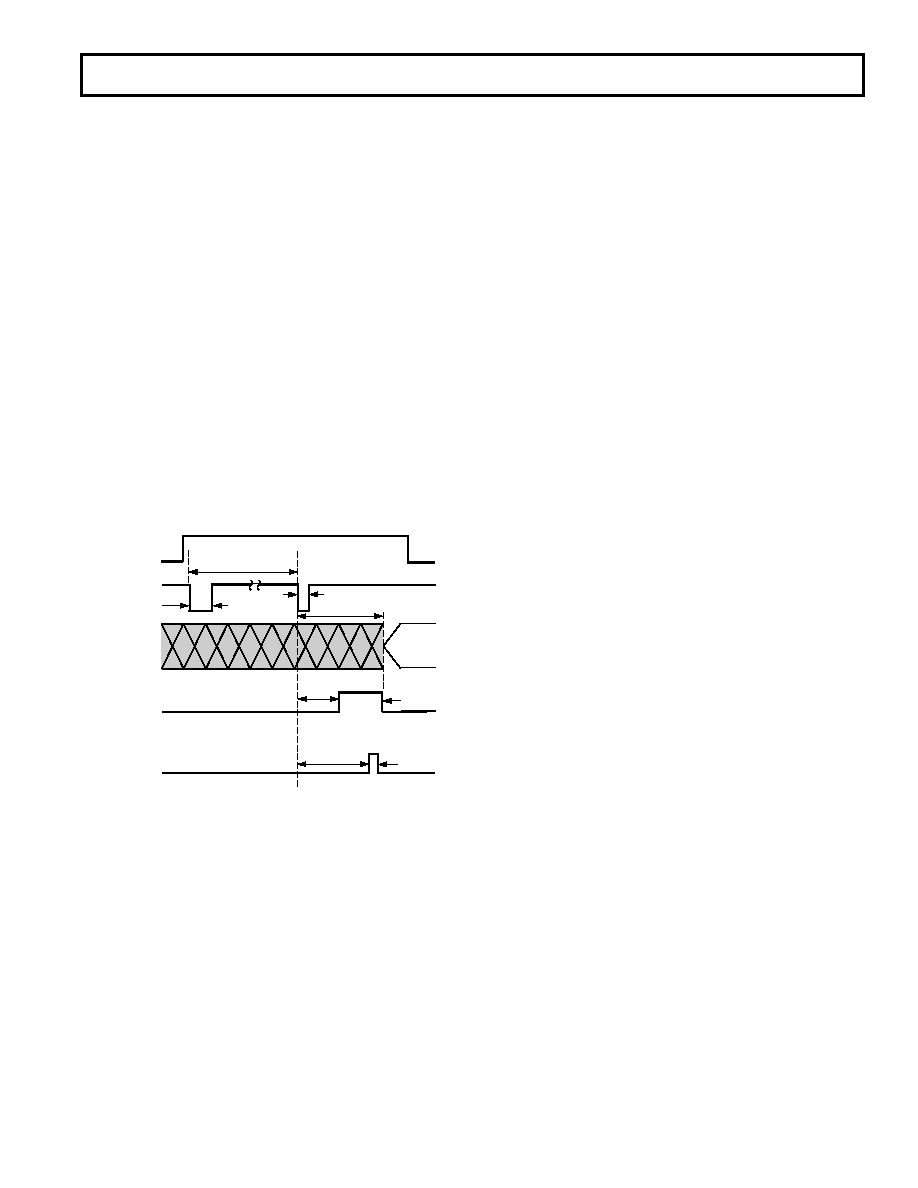

Power-Down Load Checking

One of the main uses of the TVDET signal is for plug-and-play

operation. When this feature is used, a VGA controller or other

IC polls the AD723 at regular intervals (such as once per second)

to see if a load has been attached to either output. If a load is

found, active video and sync signals can be generated for TV

encoding if CE is held.

To facilitate this use, the AD723 supports sleep-mode load

checking while powered down. This feature is activated with the

timing sequence shown in Figure 5. CE is temporarily raised

high while a single full-width horizontal sync pulse followed by a

single half-width horizontal sync pulse are applied. The spacing

between these two pulses should nominally be one H. Load check-

ing is performed just after the half-width pulse (this simulates

the beginning of the vertical blanking interval) and the TVDET

signal becomes valid approximately 18

s after the pulse’s lead-

ing edge (for both NTSC and PAL). CE is held high until TVDET

is valid and is then pulled low to avoid powering up the rest of

the chip. To make this mode possible, the AD723 is designed to

activate only the digital and sleep mode load check sections of

the IC when CE is initially pulled high. The rest of the chip is

only activated when CE remains high for four consecutive rising

edges of CSYNC.

CE

(POWER

DOWN)

CSYNC

TVDET

H = 63.5 s

TIME LEGEND:NTSC (PAL)

2.3 s

18 s

4.7 s

LOAD

CHECK

TEST

CURRENT

LOAD

CHECK

EVAL

PULSE

(8.2 s)

8.2 s

(14.3 s)

15.9 s

(7.3 s)

9.1 s

(0.9 s)

1.1 s

CE = HIGH (AWAKE/SLEEP)

Figure 5. Timing Diagram for Load Check

The advantage of this two-tiered power-up sequence is that the

total time required to poll for TV presence is kept short, and

standby power is kept low. When the entire chip is powered up,

a settling time as long as 100 ms may be required before the load

check signal becomes valid, due to settling of the input clamp. If

this settling time was part of the plug-and-play update loop, then

an on-time duty cycle of 10% would result for a load check interval

of once per second. This would result in substantial current con-

sumption. With power-down load checking, and reasonable duty

cycle, a standby current less than 1

A can be maintained.

Some important points to keep in mind when using the TVDET

signal are as follows. When power-down load check is used, the

TVDET pin reflects the status at the time of checking. The addi-

tion or removal of loads afterwards is not be reflected without

checking again. When CE is high, however, the TVDET output

will be updated about once per second, provided a valid CSYNC

signal is applied (or HSYNC and VSYNC). The TVDET output

is the logical OR of the TVDET flags for the Y and CV outputs.

Another important consideration when using the TVDET signal

is that it is temporarily invalid at full power-up while the input

dc restore circuit settles. The settling time can be up to 100 ms

for large input coupling capacitors. This means that it is not

advisable to use the TVDET signal to directly gate CE. This

arrangement may lead to a limit cycle. Suitable delay should be

included after turning the AD723 on before deciding to turn it

off again because no load is detected.

DC-Coupled Outputs

The video outputs of the AD723 (Y, C and CV) are all dc-

coupled. The advantages of this are two-fold. First, the need for

large ac-coupling capacitors (220

F typically) at the output is

eliminated. Second, it becomes possible to perform load checking.

The disadvantage with dc-coupled outputs is that there is more

dc current to dissipate. Reducing the supply voltage to 3 V can

minimize this. Here, the typical power consumption will be

similar to ac-coupled voltage drivers. As a result of dissipating

dc current, there are two different power consumption numbers:

one for a typical picture, and one for a worst-case all-white screen.

The all-white screen requires a significant amount of power to

be dissipated, but it is very uncommon for both RGB computer

graphics and video to be in this condition.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-B5L-IX-B1 | CONVERTER MOD DC/DC 28V 75W |

| MK20DX128VLF5 | IC ARM CORTEX MCU 128KB 48LQFP |

| VE-B5K-IX-B1 | CONVERTER MOD DC/DC 40V 75W |

| MCF51JE256VLL | IC MCU 32BIT 256K FLASH 100LQFP |

| VE-B5K-IW-B1 | CONVERTER MOD DC/DC 40V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD723ARUZ-REEL | 功能描述:IC ENCODER RGB-NTSC/PAL 28-TSSOP RoHS:是 类别:集成电路 (IC) >> 接口 - 编码器,解码器,转换器 系列:- 产品变化通告:Development Systems Discontinuation 26/Apr/2011 标准包装:1 系列:- 类型:编码器 应用:DVB-S.2 系统 电压 - 电源,模拟:- 电压 - 电源,数字:- 安装类型:- 封装/外壳:模块 供应商设备封装:模块 包装:散装 其它名称:Q4645799 |

| AD723ARUZ-REEL7 | 功能描述:IC ENCODER RGB-NTSC/PAL 28-TSSOP RoHS:是 类别:集成电路 (IC) >> 接口 - 编码器,解码器,转换器 系列:- 产品变化通告:Development Systems Discontinuation 26/Apr/2011 标准包装:1 系列:- 类型:编码器 应用:DVB-S.2 系统 电压 - 电源,模拟:- 电压 - 电源,数字:- 安装类型:- 封装/外壳:模块 供应商设备封装:模块 包装:散装 其它名称:Q4645799 |

| AD723-EVAL | 制造商:Analog Devices 功能描述:AD723 EVALUATION BOARD - Bulk |

| AD723WARUZ-RL7 | 功能描述:RGB to NTSC/PAL Encoder IC Video 28-TSSOP 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:有效 类型:RGB 转 NTSC/PAL 编码器 应用:视频 电压 - 电源,模拟:2.7 V ~ 5.5 V 电压 - 电源,数字:2.7 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:28-TSSOP(0.173",4.40mm 宽) 供应商器件封装:28-TSSOP 标准包装:1 |

| AD724 | 制造商:AD 制造商全称:Analog Devices 功能描述:RGB to NTSC/PAL Encoder |

发布紧急采购,3分钟左右您将得到回复。