参数资料

| 型号: | AD725ARZ-R7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/20页 |

| 文件大小: | 0K |

| 描述: | IC ENCODER RGB TO NTSC 16-SOIC |

| 标准包装: | 400 |

| 类型: | 视频编码器 |

| 应用: | RGB 至 NTSC/PAL |

| 电压 - 电源,数字: | 4.75 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 16-SOIC W |

| 包装: | 带卷 (TR) |

AD725

REV. 0

–17–

6

3

–24

0.1

10.0

1.0

0

–3

–6

–9

–12

–15

–18

–21

FREQUENCY – MHz

GAIN

–

dB

LUMA PIN

COMP PIN

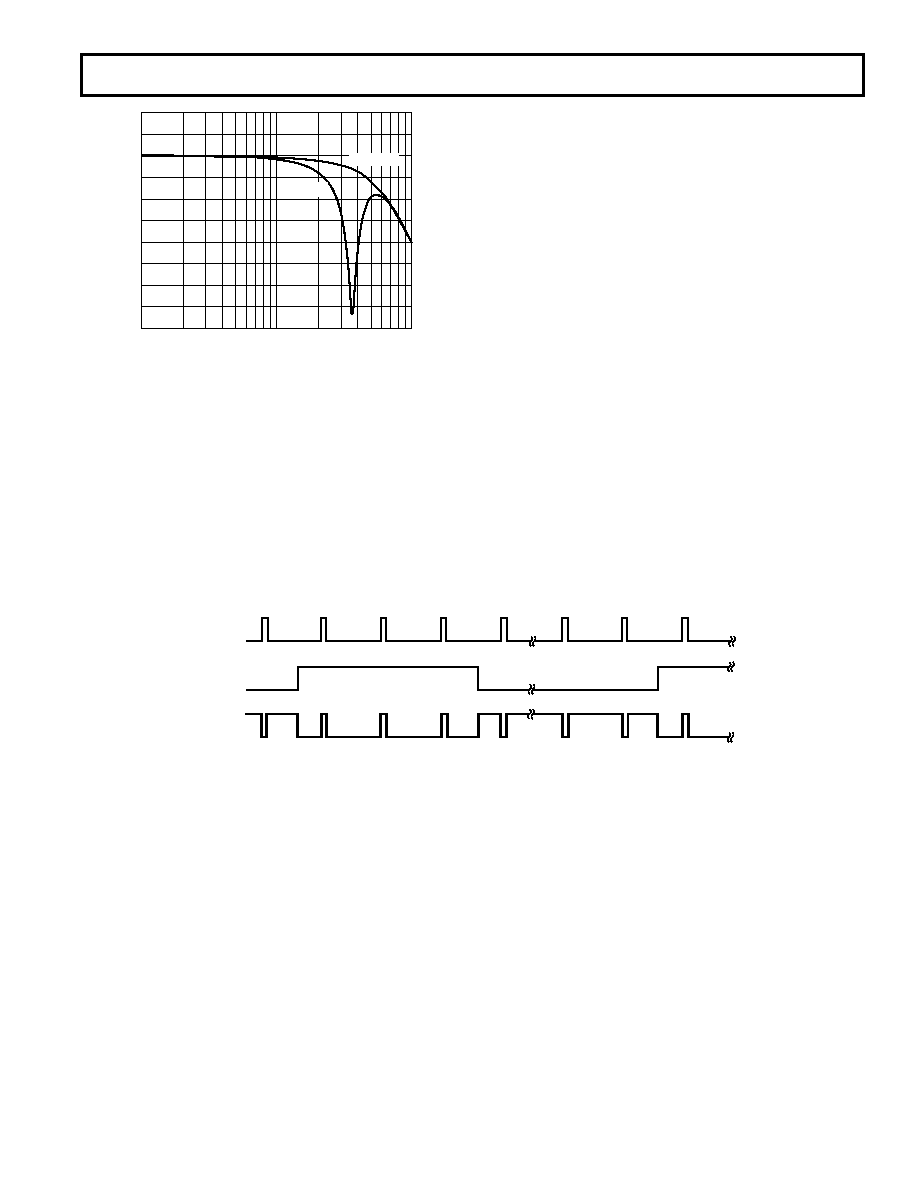

Figure 25. Luminance Frequency Response with NTSC Trap

SYNCHRONIZING SIGNALS

The AD725 requires explicit horizontal and vertical synchroniz-

ing signals for proper operation. This information cannot and

should not be incorporated in any of the RGB signals. However,

the synchronizing information can be provided as either separate

horizontal (HSYNC) and vertical (VSYNC) signals or as a

single composite sync (CSYNC) signal.

Internally the AD725 requires a composite sync logic signal that

is mostly high and goes low during horizontal sync time. The

vertical interval will have an inverted duty cycle from this. This

signal should occur at the output of an on-chip XNOR gate on

the AD725 whose two inputs are HSYNC (Pin 16) and VSYNC

(Pin 15). There are several options for meeting these conditions.

The first is to have separate signals for HSYNC and VSYNC.

Each should be mostly low and then high going during their

respective time of assertion. This is the convention used by

RGB monitors for most PCs. The proper composite sync signal

will be produced by the on-chip XNOR gate when using these

inputs.

If a composite sync signal is already available, it can be input

into HSYNC (Pin 16), while VSYNC (Pin 15) can be used to

change the polarity. (In actuality, HSYNC and VSYNC are

interchangeable since they are symmetric inputs to a two-input

gate).

If the composite sync input is mostly high and then low going

for active HSYNC time (and inverted duty cycle during VSYNC),

then it is already of the proper polarity. Pulling VSYNC high,

while inputting the composite sync signal to HSYNC will pass

this signal though the XNOR gate without inversion.

On the other hand, if the composite sync signal is the opposite

polarity as described above, pulling VSYNC low will cause the

XNOR gate to invert the signal. This will make it the proper

polarity for use inside the AD725. These logic conditions are

illustrated in Figure 26.

HSYNC

VSYNC

CSYNC

Figure 26. Sync Logic Levels (Equalization and Serration Pulses Not Shown)

相关PDF资料 |

PDF描述 |

|---|---|

| AD7294BCPZRL | IC ADC 12BIT I2C/SRL 1M 56LFCSP |

| AD7306AN | IC TXRX RS-232 RS-422 24-DIP |

| AD7339BSZ-REEL | IC ADC/QUAD DAC 5V W/REF 52-MQFP |

| AD7376ARUZ100 | IC POT DIGITAL 128POS 14-TSSOP |

| AD7391SRZ | IC DAC 10BIT SERIAL 3V 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD725ARZ-RL | 功能描述:IC ENCODER RGB TO NTSC 16-SOIC RoHS:是 类别:集成电路 (IC) >> 接口 - 编码器,解码器,转换器 系列:- 产品变化通告:Development Systems Discontinuation 26/Apr/2011 标准包装:1 系列:- 类型:编码器 应用:DVB-S.2 系统 电压 - 电源,模拟:- 电压 - 电源,数字:- 安装类型:- 封装/外壳:模块 供应商设备封装:模块 包装:散装 其它名称:Q4645799 |

| AD725ATQ | 制造商:Analog Devices 功能描述: |

| AD725EB | 制造商:Analog Devices 功能描述: |

| AD725-EB | 制造商:Analog Devices 功能描述:LOW COST RGB TO NTSC/PAL ENCODER W/ LUMA TRAP PORT - Bulk |

| AD725-EBZ | 制造商:Analog Devices 功能描述:EVALUATION BOARDS - Bulk |

发布紧急采购,3分钟左右您将得到回复。