- 您现在的位置:买卖IC网 > PDF目录10304 > AD7476AAKSZ-500RL7 (Analog Devices Inc)IC ADC 12BIT 1MSPS LP SC70-6 PDF资料下载

参数资料

| 型号: | AD7476AAKSZ-500RL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 16/29页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12BIT 1MSPS LP SC70-6 |

| 设计资源: | Output Channel Monitoring Using AD5380 (CN0008) AD5382 Channel Monitor Function (CN0012) AD5381 Channel Monitor Function (CN0013) AD5383 Channel Monitor Function (CN0015) AD5390/91/92 Channel Monitor Function (CN0030) Power off protected data acquisition signal chain using ADG4612 , AD711, and AD7476 (CN0165) |

| 标准包装: | 1 |

| 位数: | 12 |

| 采样率(每秒): | 1M |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 17.5mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 6-TSSOP,SC-88,SOT-363 |

| 供应商设备封装: | SC-70-6 |

| 包装: | 标准包装 |

| 输入数目和类型: | 1 个单端,单极 |

| 其它名称: | AD7476AAKSZ-500RL7DKR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

AD7476A/AD7477A/AD7478A

Rev. F | Page 22 of 28

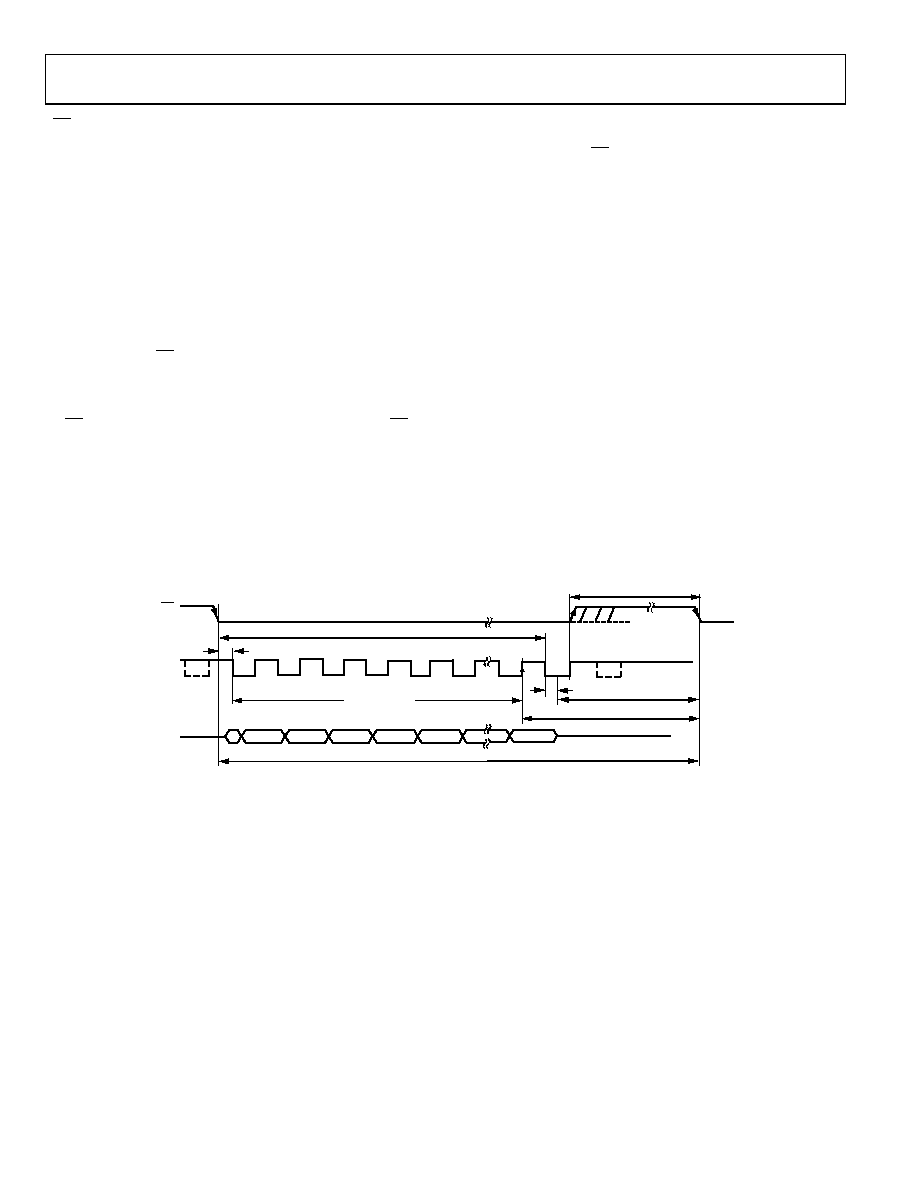

CS going low clocks out the first leading zero to be read in by

the microcontroller or DSP. The remaining data is then clocked

out by subsequent SCLK falling edges beginning with the

second leading zero. Thus, the first falling clock edge on the

serial clock has the first leading zero provided and also clocks

out the second leading zero. For the AD7476A, the final bit in

the data transfer is valid on the 16th falling edge, having been

clocked out on the previous (15th) falling edge.

In applications with a slower SCLK, it is possible to read in data

on each SCLK rising edge. In this case, the first falling edge of

SCLK clocks out the second leading zero, which can be read in

the first rising edge. However, the first leading zero that was

clocked out when CS went low will be missed, unless it was not

read in the first falling edge. The 15th falling edge of SCLK clocks

out the last bit and it can be read in the 15th rising SCLK edge.

If CS goes low just after one SCLK falling edge has elapsed, CS

clocks out the first leading zero as it did before, and it can be

read in the SCLK rising edge. The next SCLK falling edge clocks

out the second leading zero, and it can be read in the following

rising edge.

AD7478A IN A 12 SCLK CYCLE SERIAL INTERFACE

For the AD7478A, if CS is brought high in the 12th rising edge

after four leading zeros and eight bits of the conversion have

been provided, the part can achieve a 1.2 MSPS throughput

rate. For the AD7478A, the track-and-hold goes back into track

in the 11th rising edge. In this case, a fSCLK = 20 MHz and a

throughput of 1.2 MSPS give a cycle time of

t2 + 10.5(1/fSCLK)+ tACQ = 833 ns

With t2 = 10 ns min, this leaves tACQ to be 298 ns. This 298 ns

satisfies the requirement of 225 ns for tACQ.

0.5 (1/fSCLK) + t8 + tQUIET

where t8 = 36 ns maximum.

This allows a value of 237 ns for tQUIET, satisfying the minimum

requirement of 50 ns.

SCLK

t1

1

5

11

SDATA

THREE-STATE

DB7

DB6

DB0

ZERO

4 LEADING ZEROS

2

3

t2

t8

12

1/THROUGHPUT

tACQ

10.5(1/

fSCLK)

tCONVERT

tQUIET

B

THREE-STATE

CS

4

02930-027

Z

Figure 27. AD7478A in a 12 SCLK Cycle Serial Interface

相关PDF资料 |

PDF描述 |

|---|---|

| D38999/26FG11AN | CONN HSG PLUG 11POS STRGHT PINS |

| D38999/20MC8AB | CONN HSG RCPT 8POS WALL MT PINS |

| D38999/20WG11AA | CONN HSG RCPT 11POS WALL MT PINS |

| D38999/26JC98SNLC | CONN HSG PLUG 10POS STRGHT SCKT |

| MS27468T25B29PLC | CONN HSG RCPT 29POS JAMNUT PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7476AAKSZ-REEL | 功能描述:IC ADC 12BIT 1MSPS LP SC70-6 RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| AD7476AAKSZ-REEL7 | 功能描述:IC ADC 12BIT 1MSPS LP SC70-6 RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| AD7476ABKS-500RL7 | 制造商:Rochester Electronics LLC 功能描述:12-BIT LOW POWER ADC SC70 PKS I.C. - Bulk 制造商:Analog Devices 功能描述: |

| AD7476ABKS-REEL | 制造商:Analog Devices 功能描述:ADC SGL SAR 1MSPS 12-BIT SERL 6PIN SC-70 - Tape and Reel |

| AD7476ABKS-REEL7 | 制造商:Rochester Electronics LLC 功能描述:12-BIT LOW POWER ADC IN SC70 PACKAGE - Tape and Reel 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。