- 您现在的位置:买卖IC网 > PDF目录10201 > AD7663ASTZRL (Analog Devices Inc)IC ADC 16BIT CMOS 48-LQFP T/R PDF资料下载

参数资料

| 型号: | AD7663ASTZRL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 19/24页 |

| 文件大小: | 0K |

| 描述: | IC ADC 16BIT CMOS 48-LQFP T/R |

| 产品培训模块: | Power Line Monitoring |

| 标准包装: | 2,000 |

| 系列: | PulSAR® |

| 位数: | 16 |

| 采样率(每秒): | 250k |

| 数据接口: | 串行,并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 41mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 4 个单端,单极;4 个单端,双极 |

| 配用: | EVAL-AD7663CBZ-ND - BOARD EVALUATION FOR AD7663 |

REV. B

AD7663

–4–

TIMING SPECIFICATIONS (continued)

Parameter

Symbol

Min

Typ

Max

Unit

Refer to Figures 17 and 18 (Master Serial Interface Modes)

1

CS HIGH to SYNC HI-Z

t25

10

ns

CS HIGH to Internal SCLK HI-Z

t26

10

ns

CS HIGH to SDOUT HI-Z

t27

10

ns

BUSY HIGH in Master Serial Read after Convert

t28

See Table II

s

CNVST LOW to SYNC Asserted Delay

t29

1.25

s

(Master Serial Read after Convert)

SYNC Deasserted to BUSY LOW Delay

t30

25

ns

Refer to Figures 19 and 21 (Slave Serial Interface Modes)

External SCLK Setup Time

t31

5ns

External SCLK Active Edge to SDOUT Delay

t32

316

ns

SDIN Setup Time

t33

5ns

SDIN Hold Time

t34

5ns

External SCLK Period

t35

25

ns

External SCLK HIGH

t36

10

ns

External SCLK LOW

t37

10

ns

NOTES

1In serial interface modes, the SYNC, SCLK, and SDOUT timings are defined with a maximum load C

L of 10 pF; otherwise, the load is 60 pF maximum.

2In Serial Master Read during Convert Mode. See Table II for Master Read after Convert Mode.

Specifications subject to change without notice.

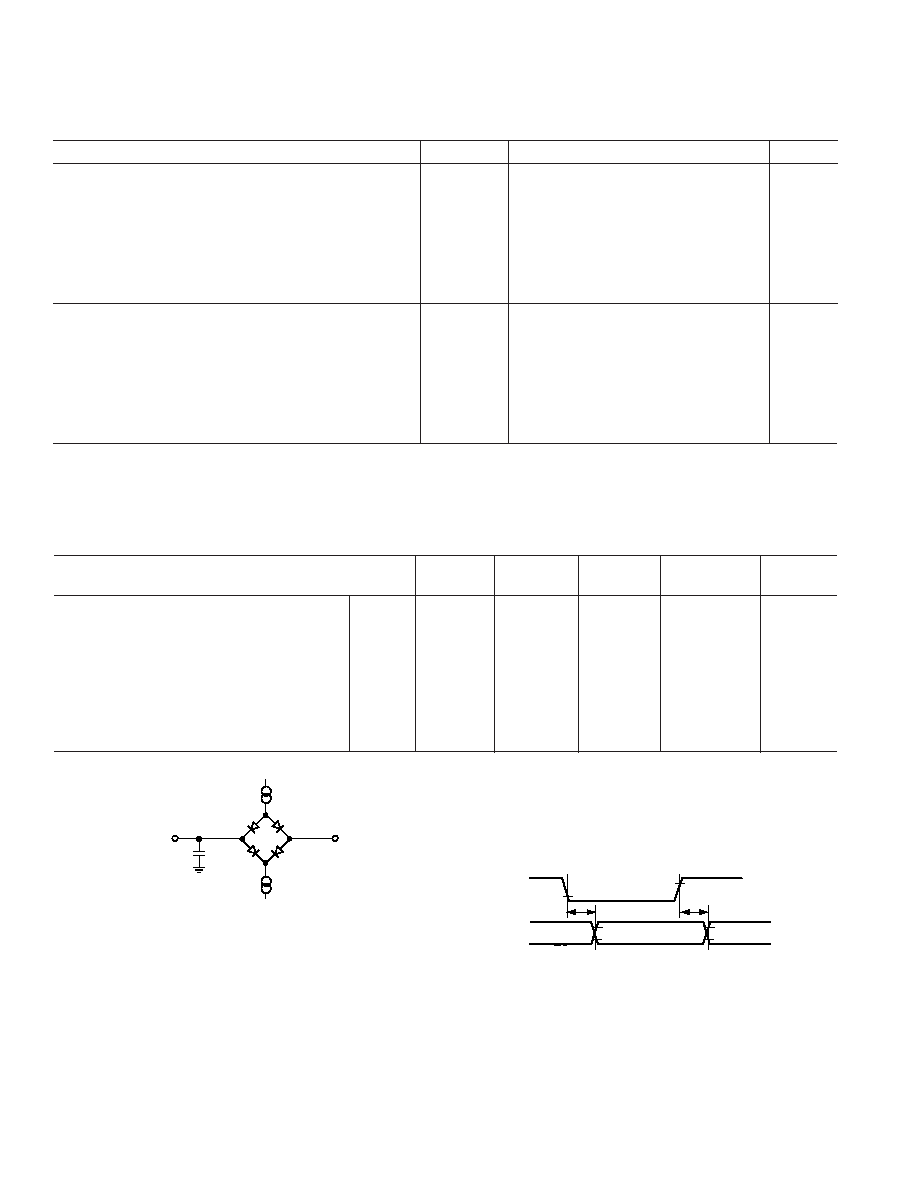

IOH

500 A

1.6mA

IOL

TO OUTPUT

PIN

1.4V

CL

60pF*

*IN SERIAL INTERFACE MODES, THE SYNC, SCLK, AND

SDOUT TIMINGS ARE DEFINED WITH A MAXIMUM LOAD

CL OF 10pF; OTHERWISE, THE LOAD IS 60pF MAXIMUM.

Figure 1. Load Circuit for Digital Interface Timing

t

DELAY

t

DELAY

0.8V

2V

Figure 2. Voltage Reference Levels for Timing

Table II. Serial Clock Timings in Master Read after Convert

DIVSCLK[1]

0011

DIVSCLK[0]

0101

Unit

SYNC to SCLK First Edge Delay Minimum

t18

420

2020

ns

Internal SCLK Period Minimum

t19

25

50

100

200

ns

Internal SCLK Period Maximum

t19

40

70

140

280

ns

Internal SCLK HIGH Minimum

t20

15

25

50

100

ns

Internal SCLK LOW Minimum

t21

9.5

24

49

99

ns

SDOUT Valid Setup Time Minimum

t22

4.5

22

ns

SDOUT Valid Hold Time Minimum

t23

2430

90

ns

SCLK Last Edge to SYNC Delay Minimum

t24

360

140

300

ns

BUSY HIGH Width Maximum

t28

2

2.5

3.5

5.75

s

相关PDF资料 |

PDF描述 |

|---|---|

| ADN4692EBRZ-RL7 | IC TXRX MLVDS 100MBPS 8SOIC |

| VE-23F-MX-F4 | CONVERTER MOD DC/DC 72V 75W |

| VE-23F-MX-F3 | CONVERTER MOD DC/DC 72V 75W |

| VE-263-CU-F4 | CONVERTER MOD DC/DC 24V 200W |

| AD7824KR-REEL | IC ADC 8BIT LC2MOS 4CH HS 24SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7663CB1 | 制造商:AD 制造商全称:Analog Devices 功能描述:16-Bit, 250 kSPS CMOS ADC |

| AD7664 | 制造商:AD 制造商全称:Analog Devices 功能描述:16-Bit, 570 kSPS CMOS ADC |

| AD7664ACP | 制造商:Analog Devices 功能描述:ADC Single SAR 570ksps 16-bit Parallel/Serial 48-Pin LFCSP EP 制造商:Analog Devices 功能描述:ADC SGL SAR 570KSPS 16BIT PARALLEL/SERL 48LFCSP EP - Trays 制造商:Rochester Electronics LLC 功能描述:16-BIT, 500KSPS CMOS ADC - Bulk |

| AD7664ACPRL | 制造商:Analog Devices 功能描述:ADC Single SAR 570ksps 16-bit Parallel/Serial 48-Pin LFCSP EP T/R |

| AD7664ACPZ | 功能描述:IC ADC 16BIT UNIPOLAR 48-LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:PulSAR® 其它有关文件:TSA1204 View All Specifications 标准包装:1 系列:- 位数:12 采样率(每秒):20M 数据接口:并联 转换器数目:2 功率耗散(最大):155mW 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-TQFP 供应商设备封装:48-TQFP(7x7) 包装:Digi-Reel® 输入数目和类型:4 个单端,单极;2 个差分,单极 产品目录页面:1156 (CN2011-ZH PDF) 其它名称:497-5435-6 |

发布紧急采购,3分钟左右您将得到回复。