- 您现在的位置:买卖IC网 > PDF目录10292 > AD7705BRZ-REEL7 (Analog Devices Inc)IC ADC 16BIT 2CHAN 16SOIC PDF资料下载

参数资料

| 型号: | AD7705BRZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/44页 |

| 文件大小: | 0K |

| 描述: | IC ADC 16BIT 2CHAN 16SOIC |

| 标准包装: | 1 |

| 位数: | 16 |

| 采样率(每秒): | 500 |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 1mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 16-SOIC W |

| 包装: | 标准包装 |

| 输入数目和类型: | 2 个差分,单极;2 个差分,双极 |

| 其它名称: | AD7705BRZ-REEL7DKR |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

AD7705/AD7706

Rev. C | Page 17 of 44

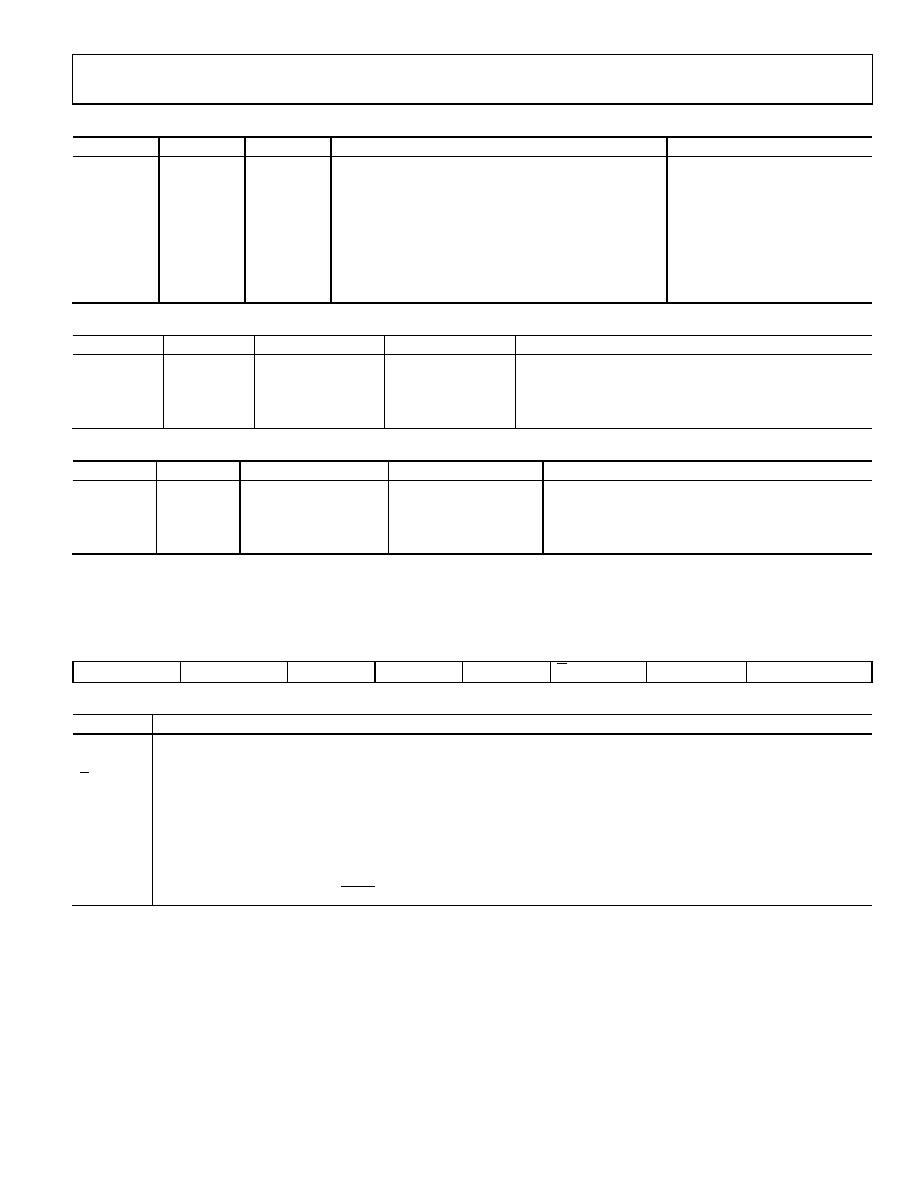

Table 11. Register Selection

RS2

RS1

RS0

Register

Register Size

0

Communication register

8 bits

0

1

Setup register

8 bits

0

1

0

Clock register

8 bits

0

1

Data register

16 bits

1

0

Test register

8 bits

1

0

1

No operation

1

0

Offset register

24 bits

1

Gain register

24 bits

Table 12. Channel Selection for AD7705

CH1

CH0

AIN(+)

AIN()

Calibration Register Pair

0

AIN1(+)

AIN1()

Register Pair 0

0

1

AIN2(+)

AIN2()

Register Pair 1

1

0

AIN1()

Register Pair 0

1

AIN1()

AIN2()

Register Pair 2

Table 13. Channel Selection for AD7706

CH1

CH0

AIN

Reference

Calibration Register Pair

0

AIN1

COMMON

Register Pair 0

0

1

AIN2

COMMON

Register Pair 1

1

0

COMMON

Register Pair 0

1

AIN3

COMMON

Register Pair 2

SETUP REGISTER (RS2, RS1, RS0 = 0, 0, 1); POWER-ON/RESET STATUS: 01 HEXADECIMAL

The setup register is an 8-bit register from which data can be read or to which data can be written.

Table 14 outlines the bit designations for the setup register.

Table 14. Setup Register

MD1 (0)

MD0 (0)

G2 (0)

G1 (0)

G0 (0)

B/U (0)

BUF (0)

FSYNC (1)

Table 15. Setup Register Description

Register

Description

MD1, MD0

ADC Mode Bits. These bits select the operational mode of the ADC as outlined in Table 16.

G2 to G0

Gain Selection Bits. These bits select the gain setting for the on-chip PGA, as outlined in Table 17.

B/U

Bipolar/Unipolar Operation. A 0 in this bit selects bipolar operation; a 1 in this bit selects unipolar operation.

BUF

Buffer Control. With this bit at 0, the on-chip buffer on the analog input is shorted out. With the buffer shorted out, the current

flowing in the VDD line is reduced. When this bit is high, the on-chip buffer is in series with the analog input, allowing the input

to handle higher source impedances.

FSYNC

Filter Synchronization. When this bit is high, the nodes of the digital filter, the filter control logic, the calibration control logic,

and the analog modulator are held in a reset state. When this bit goes low, the modulator and filter start to process data, and

a valid word is available in 3 × 1/output rate, that is, the settling time of the filter. This FSYNC bit does not affect the digital

interface and does not reset the DRDY output if it is low.

相关PDF资料 |

PDF描述 |

|---|---|

| MS27467T15F18PA | CONN PLUG 18POS STRAIGHT W/PINS |

| D38999/20JG75BN | CONN HSG RCPT 4POS WALL MT SCKT |

| D38999/26MB99SNLC | CONN HSG PLUG 7POS STRGHT SCKT |

| AD7888BR-REEL7 | IC ADC 12BIT 8CHAN SRL 16SOIC |

| D38999/26WG11AB | CONN HSG PLUG 11POS STRGHT PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7705BRZ-REEL71 | 制造商:AD 制造商全称:Analog Devices 功能描述:3 V/5 V, 1 mW, 2-/3-Channel, 16-Bit, Sigma-Delta ADCs |

| AD7705EB | 制造商:AD 制造商全称:Analog Devices 功能描述:3 V/5 V 1 mW 2-/3-Channel 16-Bit Sigma-Delta ADCs(264.12 k) |

| AD7706 | 制造商:AD 制造商全称:Analog Devices 功能描述:3 V/5 V, 1 mW 2-/3-Channel 16-Bit, Sigma-Delta ADCs |

| AD7706BN | 功能描述:IC ADC 16BIT 3CH 16-DIP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:12 采样率(每秒):3M 数据接口:- 转换器数目:- 功率耗散(最大):- 电压电源:- 工作温度:- 安装类型:表面贴装 封装/外壳:SOT-23-6 供应商设备封装:SOT-23-6 包装:带卷 (TR) 输入数目和类型:- |

发布紧急采购,3分钟左右您将得到回复。