- 您现在的位置:买卖IC网 > PDF目录10278 > AD7718BR-REEL (Analog Devices Inc)IC ADC 24BIT R-R 8/10CH 28-SOIC PDF资料下载

参数资料

| 型号: | AD7718BR-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 7/44页 |

| 文件大小: | 0K |

| 描述: | IC ADC 24BIT R-R 8/10CH 28-SOIC |

| 标准包装: | 1,000 |

| 位数: | 24 |

| 采样率(每秒): | 1.37k |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 3.84mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 28-SOIC W |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 5 个差分,单极;5 个差分,双极;10 伪差分,单极;10 伪差分,双极 |

| 配用: | EVAL-AD7718EBZ-ND - BOARD EVALUATION FOR AD7718 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

REV. 0

AD7708/AD7718

–15–

ADC CIRCUIT INFORMATION

The AD7708/AD7718 incorporates a 10-channel multiplexer

with a sigma-delta ADC, on-chip programmable gain amplifier

and digital filtering intended for the measurement of wide

dynamic range, low frequency signals such as those in weigh-scale,

strain-gauge, pressure transducer, or temperature measurement

applications. The AD7708 offers 16-bit resolution while the

AD7718 offers 24-bit resolution. The AD7718 is a pin-for-pin

compatible version of the AD7708. The AD7718 offers a direct

upgradable path from a 16-bit to a 24-bit system without requiring

any hardware changes and only minimal software changes.

These parts can be configured as four/five fully-differential

input channels or as eight/ten pseudo-differential input chan-

nels referenced to AINCOM. The channel is buffered and can

be programmed for one of eight input ranges from

±20 mV to

±2.56 V. Buffering the input channel means that the part can

handle significant source impedances on the analog input and

that R, C filtering (for noise rejection or RFI reduction) can be

placed on the analog inputs if required. These input channels

are intended to convert signals directly from sensors without the

need for external signal conditioning.

The ADC employs a sigma-delta conversion technique to realize

up to 24 bits of no missing codes performance. The sigma-delta

modulator converts the sampled input signal into a digital pulse

train whose duty cycle contains the digital information. A Sinc

3

programmable low-pass filter is then employed to decimate the

modulator output data stream to give a valid data conversion result

at programmable output rates. The signal chain has two modes

of operation, CHOP enabled and CHOP disabled. The

CHOP bit

in the mode register enables and disables the chopping scheme.

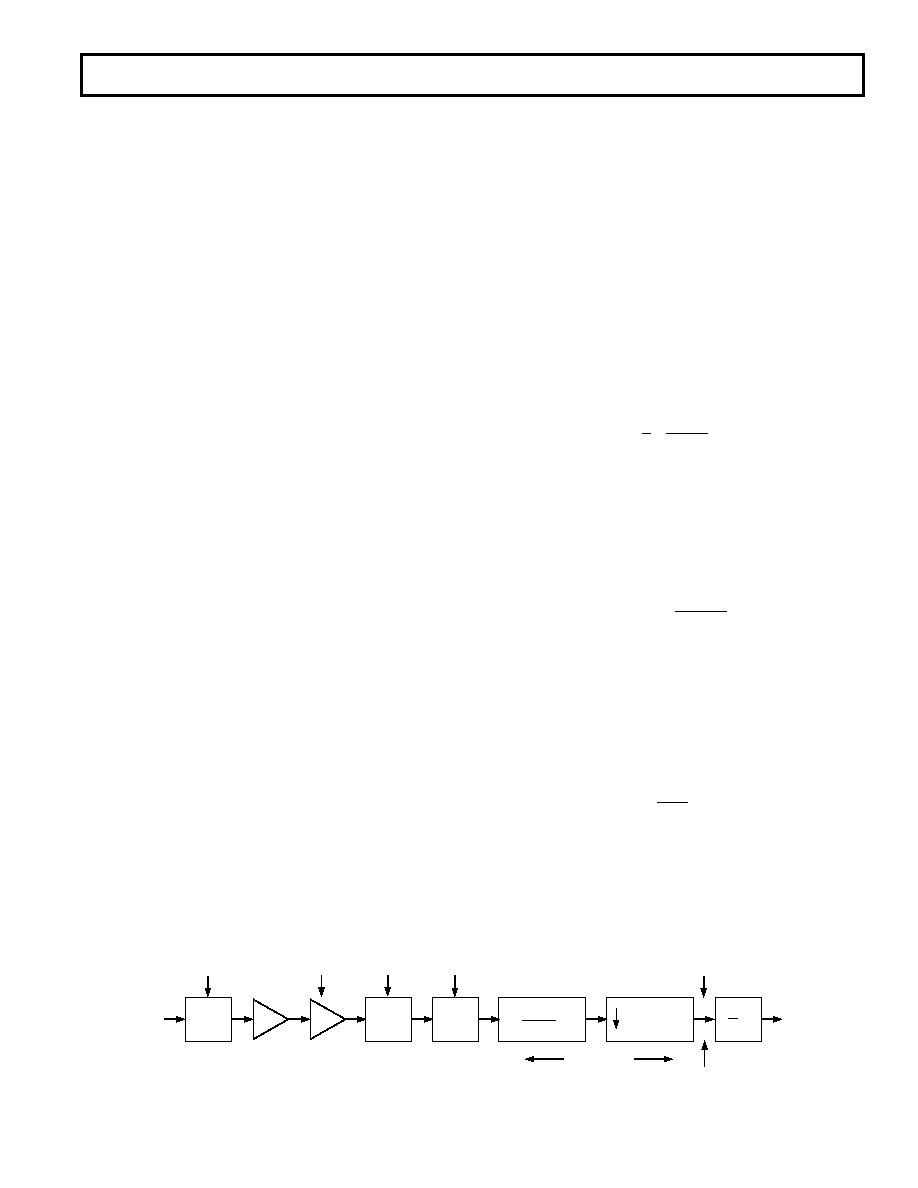

Signal Chain Overview (CHOP Enabled, CHOP = 0)

With CHOP = 0, chopping is enabled, this is the default and gives

optimum performance in terms of drift performance. With chopping

enabled, the available output rates vary from 5.35 Hz (186.77 ms)

to 105.03 Hz (9.52 ms). A block diagram of the ADC input

channel with chop enabled is shown in Figure 4.

The sampling frequency of the modulator loop is many times

higher than the bandwidth of the input signal. The integrator in

the modulator shapes the quantization noise (which results from

the analog-to-digital conversion) so that the noise is pushed

toward one-half of the modulator frequency. The output of the

sigma-delta modulator feeds directly into the digital filter. The

digital filter then band-limits the response to a frequency signifi-

cantly lower than one-half of the modulator frequency. In this

manner, the 1-bit output of the comparator is translated into a

band limited, low noise output from the AD7708/AD7718 ADC.

The AD7708/AD7718 filter is a low-pass, Sinc

3 or (sinx/x)3

filter whose primary function is to remove the quantization noise

introduced at the modulator. The cutoff frequency and deci-

mated output data rate of the filter are programmable via the SF

word loaded to the filter register. The complete signal chain is

chopped resulting in excellent dc offset and offset drift specifica-

tions and is extremely beneficial in applications where drift, noise

rejection, and optimum EMI rejection are important factors.

With chopping, the ADC repeatedly reverses its inputs. The

decimated digital output words from the Sinc

3 filters, therefore,

have a positive offset and negative offset term included. As a

result, a final summing stage is included so that each output

word from the filter is summed and averaged with the previous

filter output to produce a new valid output result to be written

to the ADC data register. The programming of the Sinc

3 deci-

mation factor is restricted to an 8-bit register SF, the actual

decimation factor is the register value times 8. The decimated

output rate from the Sinc

3 filter (and the ADC conversion rate)

will therefore be

f

SF

f

ADC

MOD

=×

×

1

3

1

8

where

fADC in the ADC conversion rate.

SF is the decimal equivalent of the word loaded to the filter

register.

fMOD is the modulator sampling rate of 32.768 kHz.

The chop rate of the channel is half the output data rate:

f

CHOP

ADC

=

×

1

2

As shown in the block diagram, the Sinc

3 filter outputs alter-

nately contain +VOS and –VOS, where VOS is the respective

channel offset. This offset is removed by performing a running

average of two. This average by two means that the settling time

to any change in programming of the ADC will be twice the

normal conversion time, while an asynchronous step change on

the analog input will not be fully reflected until the third subse-

quent output.

t

f

t

SETTLE

ADC

== ×

2

The allowable range for SF is 13 to 255 with a default of 69

(45H). The corresponding conversion rates, conversion times,

and settling times are shown in Table I. Note that the conver-

sion time increases by 0.732 ms for each increment in SF.

SINC 3 FILTER

MUX

BUF

PGA

-

MOD0

XOR

ANALOG

INPUT

DIGITAL

OUTPUT

1

8

SF

3

(8

SF )

3

1

2

AIN + VOS

AIN – VOS

f

CHOP

f

IN

f

MOD

f

CHOP

f

ADC

(

Figure 4. ADC Channel Block Diagram with CHOP Enabled

相关PDF资料 |

PDF描述 |

|---|---|

| D38999/24WJ24BN | CONN HSG RCPT 24POS JAM NUT SCKT |

| D38999/20KC98AN | CONN HSG RCPT 10POS WALL MT PINS |

| MS27473T10A99PB | CONN PLUG 7POS STRAIGHT W/PINS |

| AD7495BRZ-REEL7 | IC ADC 12BIT SRL LP W/REF 8-SOIC |

| SL404MX | CONN PLUG 4POS MALE W/COUPLING |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7718BR-REEL7 | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 1.365ksps 24-bit Serial 28-Pin SOIC W T/R 制造商:Analog Devices 功能描述:ADC SGL DELTA-SIGMA 1.365KSPS 24BIT SERL 28SOIC W - Tape and Reel 制造商:Rochester Electronics LLC 功能描述:4/5 CHNL DIFF OR 8/10 CHNL 24-BIT ADC - Tape and Reel |

| AD7718BRU | 功能描述:IC ADC 24BIT R-R 8/10CH 28-TSSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD7718BRU-REEL | 功能描述:IC ADC 24BIT R-R 8/10CH 28-TSSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| AD7718BRU-REEL7 | 功能描述:IC ADC 24BIT R-R 8/10CH 28-TSSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:12 采样率(每秒):3M 数据接口:- 转换器数目:- 功率耗散(最大):- 电压电源:- 工作温度:- 安装类型:表面贴装 封装/外壳:SOT-23-6 供应商设备封装:SOT-23-6 包装:带卷 (TR) 输入数目和类型:- |

| AD7718BRUZ | 功能描述:IC ADC 24BIT R-R 8/10CH 28-TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:microPOWER™ 位数:8 采样率(每秒):1M 数据接口:串行,SPI? 转换器数目:1 功率耗散(最大):- 电压电源:模拟和数字 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:24-VFQFN 裸露焊盘 供应商设备封装:24-VQFN 裸露焊盘(4x4) 包装:Digi-Reel® 输入数目和类型:8 个单端,单极 产品目录页面:892 (CN2011-ZH PDF) 其它名称:296-25851-6 |

发布紧急采购,3分钟左右您将得到回复。