- 您现在的位置:买卖IC网 > PDF目录10756 > AD7730BRUZ (Analog Devices Inc)IC ADC TRANSDUCER BRIDGE 24TSSOP PDF资料下载

参数资料

| 型号: | AD7730BRUZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/53页 |

| 文件大小: | 0K |

| 描述: | IC ADC TRANSDUCER BRIDGE 24TSSOP |

| 标准包装: | 1 |

| 位数: | 24 |

| 通道数: | 1 |

| 功率(瓦特): | 125mW |

| 电压 - 电源,模拟: | 4.75 V ~ 5.25 V |

| 电压 - 电源,数字: | 2.7 V ~ 5.25 V |

| 封装/外壳: | 24-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 24-TSSOP |

| 包装: | 管件 |

| 产品目录页面: | 778 (CN2011-ZH PDF) |

| 配用: | EVAL-AD7730LEBZ-ND - BOARD EVALUATION FOR AD7730 EVAL-AD7730EBZ-ND - BOARD EVAL FOR AD7730 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页

AD7730/AD7730L

–19–

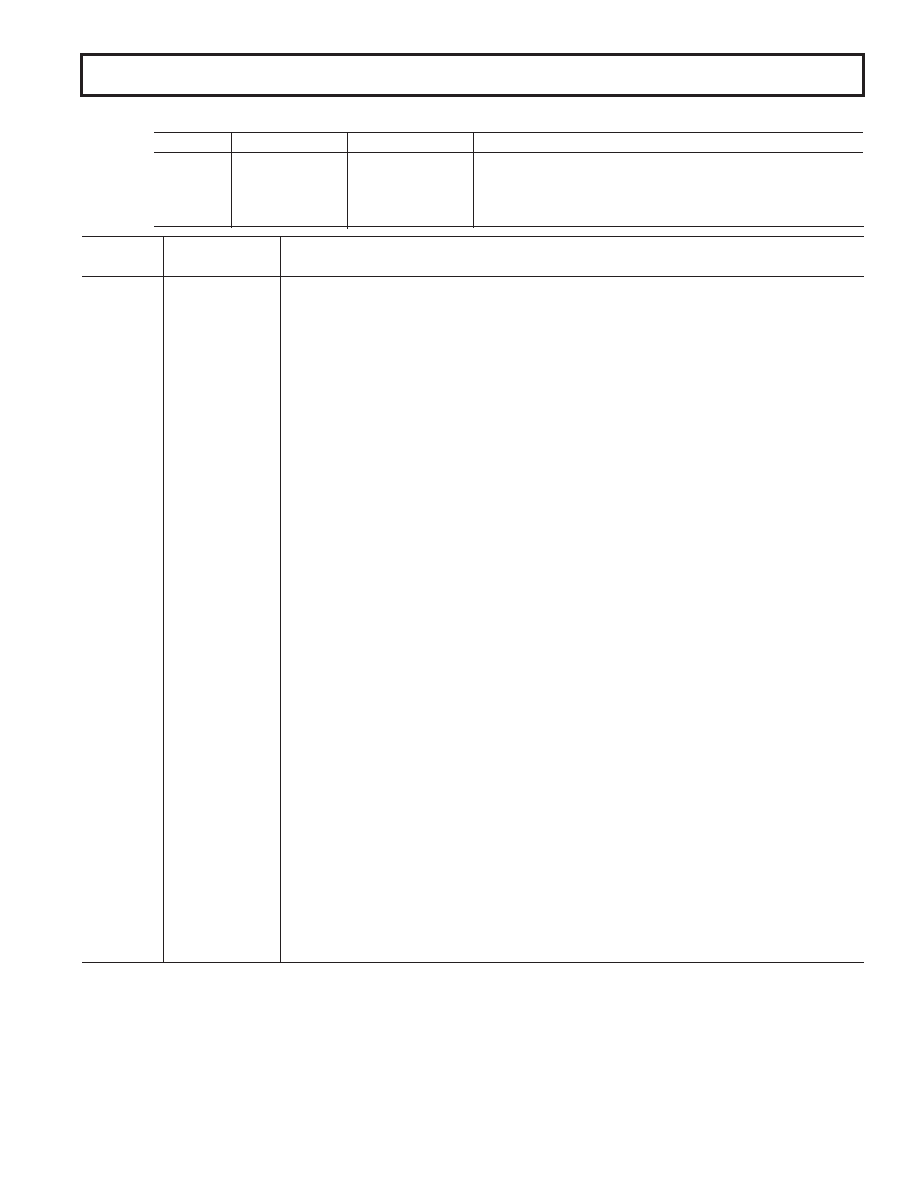

Table XV. SF Ranges

CHOP

SKIP

SF Range

Output Update Rate Range (Assuming 4.9152 MHz Clock)

0

2048 to 150

150 Hz to 2.048 kHz

1

0

2048 to 75

50 Hz to 1.365 kHz

0

1

2048 to 40

150 Hz to 7.6 kHz

1

2048 to 20

50 Hz to 5.12 kHz

Bit

Location

Mnemonic

Description

FR11–FR10

ZERO

A zero must be written to these bits to ensure correct operation of the AD7730.

FR9

SKIP

FIR Filter Skip Bit. With a 0 in this bit, the AD7730 performs two stages of filtering before

shipping a result out of the filter. The first is a sinc3 filter followed by a 22-tap FIR filter. With a

1 in this bit, the FIR filter on the part is bypassed and the output of the sinc3 is fed directly

as the output result of the AD7730’s filter (see Filter Architecture for more details on the filter

implementation).

FR8

FAST

FASTStep Mode Enable Bit. A 1 in this bit enables the FASTStep mode on the AD7730. In

this mode, if a step change on the input is detected, the FIR calculation portion of the filter is

suspended and replaced by a simple moving average on the output of the sinc3 filter. Initially,

two outputs from the sinc3 filter are used to calculate an AD7730 output. The number of sinc3

outputs used to calculate the moving average output is increased (from 2 to 4 to 8 to 16) until

the

STDY bit goes low. When the FIR filter has fully settled after a step, the STDY bit will

become active and the FIR filter is switched back into the processing loop (see Filter Architec-

ture section for more details on the FASTStep mode).

FR7–FR6

ZERO

A zero must be written to these bits to ensure correct operation of the AD7730.

FR5

AC

AC Excitation Bit. If the signal source to the AD7730 is ac-excited, a 1 must be placed in this

bit. For dc-excited inputs, this bit must be 0. The ac bit has no effect if CHP is 0. With the ac

bit at 1, the AD7730 assumes that the voltage at the AIN(+)/AIN(–) and REF IN(+)/REF IN(–)

input terminals are reversed on alternate input sampling cycles (i.e. chopped). Note that when

the AD7730 is performing internal zero-scale or full-scale calibrations, the ac bit is treated as a

0, i.e., the device performs these self-calibrations with dc excitation.

FR4

CHP

Chop Enable Bit. This bit determines if the chopping mode on the part is enabled. A 1 in this

bit location enables chopping on the part. When the chop mode is enabled, the part is effectively

chopped at its input and output to remove all offset and offset drift errors on the part. If offset

performance with time and temperature are important parameters in the design, it is recom-

mended that the user enable chopping on the part. If the input signal is dc-excited, the user has

the option of operating the part in either chop or nonchop mode. If the input signal is ac-excited,

both the ac bit and the CHP bit must be set to 1. The chop rate on the ACX and

ACX signals is

one half of the programmed output rate of the part and thus the chopping frequency varies with

the programmed output rate.

FR3–FR0

DL3–DL0

Delay Selection Bits. These four bits program the delay (in modulator cycles) to be inserted after

each chop edge when the CHP bit is 1. One modulator cycle is MCLK IN/16 and is 3.25

μs at

MCLK IN = 4.9152 MHz. A delay should only be required when in ac mode. Its purpose is to

cater for external delays between the switching signals (ACX and

ACX) and when the analog

inputs are actually switched and settled. During the specified number of cycles (between 0 and

15), the modulator is held in reset and the filter does not accept any inputs. If CHP = 1, the

output rate is (MCLK IN/ 16

× (DL + 3 × SF) where DL is the value loaded to bits DL0–DL3.

The chop rate is always one half of the output rate. This chop period takes into account the

programmed delay and the fact that the sinc3 filter must settle every chop cycle. With CHP = 0,

the output rate is 1/SF.

REV. B

相关PDF资料 |

PDF描述 |

|---|---|

| AD7730BRZ | IC ADC BRIDGE TRANSDUCER 24-SOIC |

| VE-J5F-MW-F2 | CONVERTER MOD DC/DC 72V 100W |

| AD7730LBRZ | IC ADC TRANSDUCER BRIDGE 24SOIC |

| AD73311ARZ | IC PROCESSOR FRONT END LP 20SOIC |

| VE-J5F-MW-F1 | CONVERTER MOD DC/DC 72V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7730BRUZ-REEL | 功能描述:IC ADC BRIDGE TRANSDUCER 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7730BRUZ-REEL7 | 功能描述:IC ADC BRIDGE TRANSDUCER 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7730BRZ | 功能描述:IC ADC BRIDGE TRANSDUCER 24-SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7730BRZ | 制造商:Analog Devices 功能描述:IC, ADC, 24BIT, 1.2KSPS, SOIC-24 |

| AD7730BRZ-REEL | 功能描述:IC ADC BRDGE TRANSDCR 24SOIC TR RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。