- 您现在的位置:买卖IC网 > PDF目录10744 > AD7730BRZ-REEL (Analog Devices Inc)IC ADC BRDGE TRANSDCR 24SOIC TR PDF资料下载

参数资料

| 型号: | AD7730BRZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 33/53页 |

| 文件大小: | 0K |

| 描述: | IC ADC BRDGE TRANSDCR 24SOIC TR |

| 标准包装: | 1,000 |

| 位数: | 24 |

| 通道数: | 1 |

| 功率(瓦特): | 125mW |

| 电压 - 电源,模拟: | 4.75 V ~ 5.25 V |

| 电压 - 电源,数字: | 2.7 V ~ 5.25 V |

| 封装/外壳: | 24-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 24-SOIC W |

| 包装: | 带卷 (TR) |

| 配用: | EVAL-AD7730LEBZ-ND - BOARD EVALUATION FOR AD7730 EVAL-AD7730EBZ-ND - BOARD EVAL FOR AD7730 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页当前第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页

AD7730/AD7730L

–39–

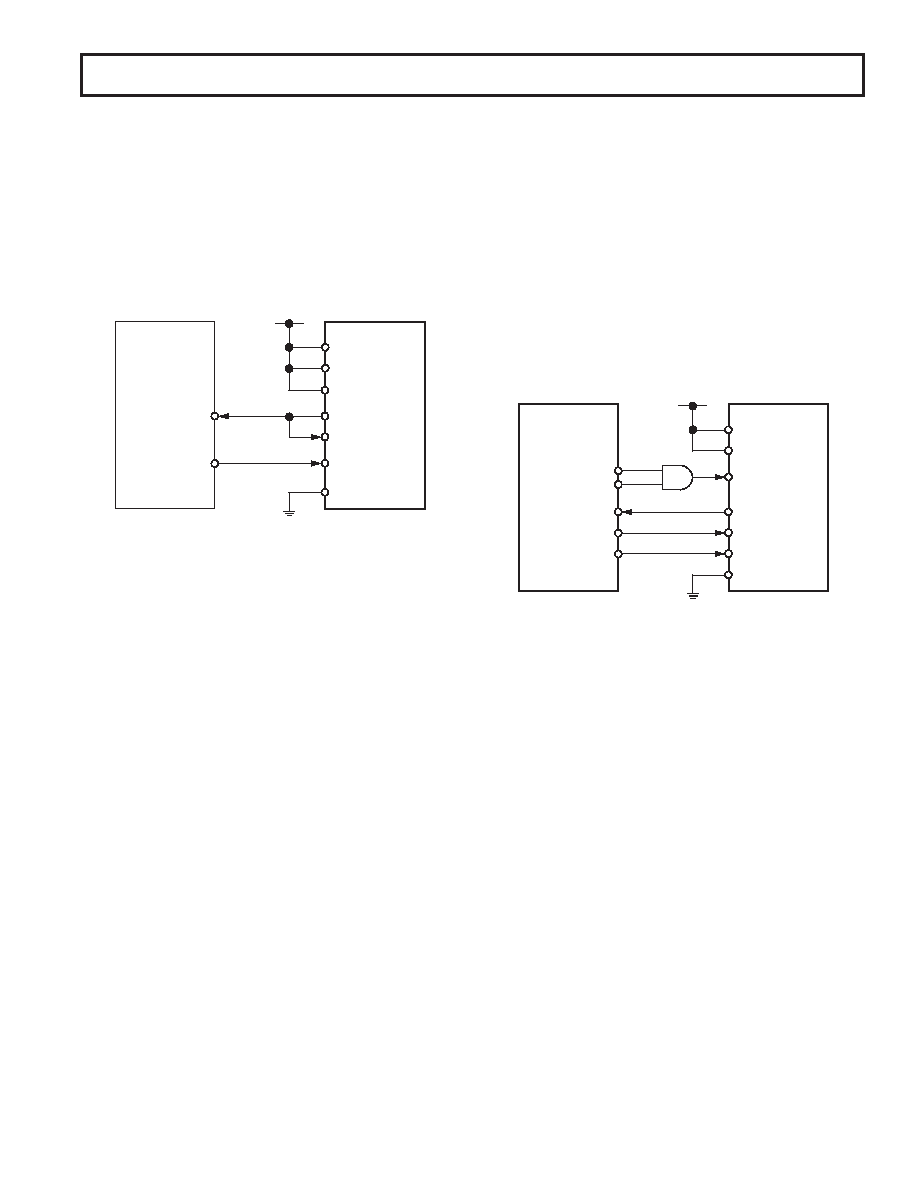

configured for continuous read operation when interfacing to

the 8XC51. The serial clock on the 8XC51 idles high between data

transfers and therefore the POL input of the AD7730 should be

hardwired to a logic high. The 8XC51 outputs the LSB first in a

write operation while the AD7730 expects the MSB first so the

data to be transmitted has to be rearranged before being written

to the output serial register. Similarly, the AD7730 outputs the

MSB first during a read operation while the 8XC51 expects the

LSB first. Therefore, the data read into the serial buffer needs to

be rearranged before the correct data word from the AD7730 is

available in the accumulator.

SYNC

RESET

AD7730

POL

DATA OUT

DATA IN

SCLK

CS

P3.0

P3.1

8XC51

DVDD

Figure 21. AD7730 to 8XC51 Interface

AD7730 to ADSP-2103/ADSP-2105 Interface

Figure 22 shows an interface between the AD7730 and the

ADSP-2105 DSP processor. In the interface shown, the

RDY

bit of the Status Register is again monitored to determine when

the Data Register is updated. The alternative scheme is to use

an interrupt driven system, in which case the

RDY output is

connected to the

IRQ2 input of the ADSP-2105. The RFS and

TFS pins of the ADSP-2105 are configured as active low out-

puts and the ADSP-2105 serial clock line, SCLK, is also config-

ured as an output. The POL pin of the AD7730 is hardwired

low. Because the SCLK from the ADSP-2105 is a continuous

clock, the

CS of the AD7730 must be used to gate off the clock

once the transfer is complete. The

CS for the AD7730 is active

when either the

RFS or TFS outputs from the ADSP-2105 are

active. The serial clock rate on the ADSP-2105 should be lim-

ited to 3 MHz to ensure correct operation with the AD7730.

SYNC

RESET

AD7730

DATA OUT

DATA IN

SCLK

CS

DR

SCLK

ADSP-2105

DVDD

RFS

TFS

DT

POL

Figure 22. AD7730 to ADSP-2105 Interface

REV. B

相关PDF资料 |

PDF描述 |

|---|---|

| MAX9144EUD+ | IC COMPARATOR R-R 14TSSOP |

| MAX9144ESD+ | IC COMPARATOR QUAD R-R HS 14SOIC |

| MAX999EUK+T | IC COMP BEYOND-THE-RAILS SOT23-5 |

| VI-B3X-IV | CONVERTER MOD DC/DC 5.2V 150W |

| VI-JNZ-MY-F1 | CONVERTER MOD DC/DC 2V 20W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7730BRZ-REEL7 | 功能描述:IC ADC BRDGE TRANSDCR 24SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7730L | 制造商:AD 制造商全称:Analog Devices 功能描述:Bridge Transducer ADC |

| AD7730LBR | 功能描述:IC ADC TRANSDUCER BRIDGE 24SOIC RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD7730LBR-REEL | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 600sps 24-bit Serial 24-Pin SOIC W T/R 制造商:Analog Devices 功能描述:ADC SGL DELTA-SIGMA 0.6KSPS 24BIT SERL 24SOIC W - Tape and Reel |

| AD7730LBR-REEL7 | 功能描述:IC ADC TRANSDUCER BRIDGE 24SOIC RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。