- 您现在的位置:买卖IC网 > PDF目录10791 > AD8123ACPZ-R7 (Analog Devices Inc)IC RCVR TRPL DIFF EQUAL 40LFCSP PDF资料下载

参数资料

| 型号: | AD8123ACPZ-R7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 3/16页 |

| 文件大小: | 0K |

| 描述: | IC RCVR TRPL DIFF EQUAL 40LFCSP |

| 标准包装: | 1 |

| 类型: | 接收器 |

| 驱动器/接收器数: | 0/3 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP-VQ(6x6) |

| 包装: | 标准包装 |

| 产品目录页面: | 765 (CN2011-ZH PDF) |

| 其它名称: | AD8123ACPZ-R7DKR |

AD8123

Rev. A | Page 11 of 16

APPLICATIONS INFORMATION

BASIC OPERATION

The AD8123 is easy to apply because it contains everything

on-chip needed for cable loss compensation. Figure 20 shows a

basic application circuit (power supplies not shown) with

common-mode sync pulse extraction that is compatible with

the common-mode sync pulse encoding technique used in the

sync extraction is not required, the terminations can be single

100 Ω resistors, and the comparator inputs can be left floating.

In Figure 20, the AD8123 is feeding a high impedance input,

such as a delay line or crosspoint switch, and the additional gain

of two that makes up for double termination loss is not required.

COMPARATORS

In addition to general-purpose applications, the two on-chip

comparators can be used to extract video sync pulses from the

received common-mode voltages or to receive differential digital

information. Built-in hysteresis helps to eliminate false triggers

from noise. The Sync Pulse Extraction Using Comparators

section describes the sync extraction details.

The comparator outputs have nearly 0 Ω output impedance and

are designed to drive source-terminated transmission lines. The

source termination technique uses a resistor in series with each

comparator output such that the sum of the comparator source

resistance (≈0 Ω) and the series resistor equals the transmission

line characteristic impedance. The load end of the transmission

line is high impedance. When the signal is launched into the source

termination, its initial value is one-half of its source value because

its amplitude is divided by two in the voltage divider formed by

the source termination and the transmission line. At the load,

the signal experiences nearly 100% positive reflection due to the

high impedance load and is restored to nearly its full value. This

technique is commonly used in PCB layouts that involve high

speed digital logic.

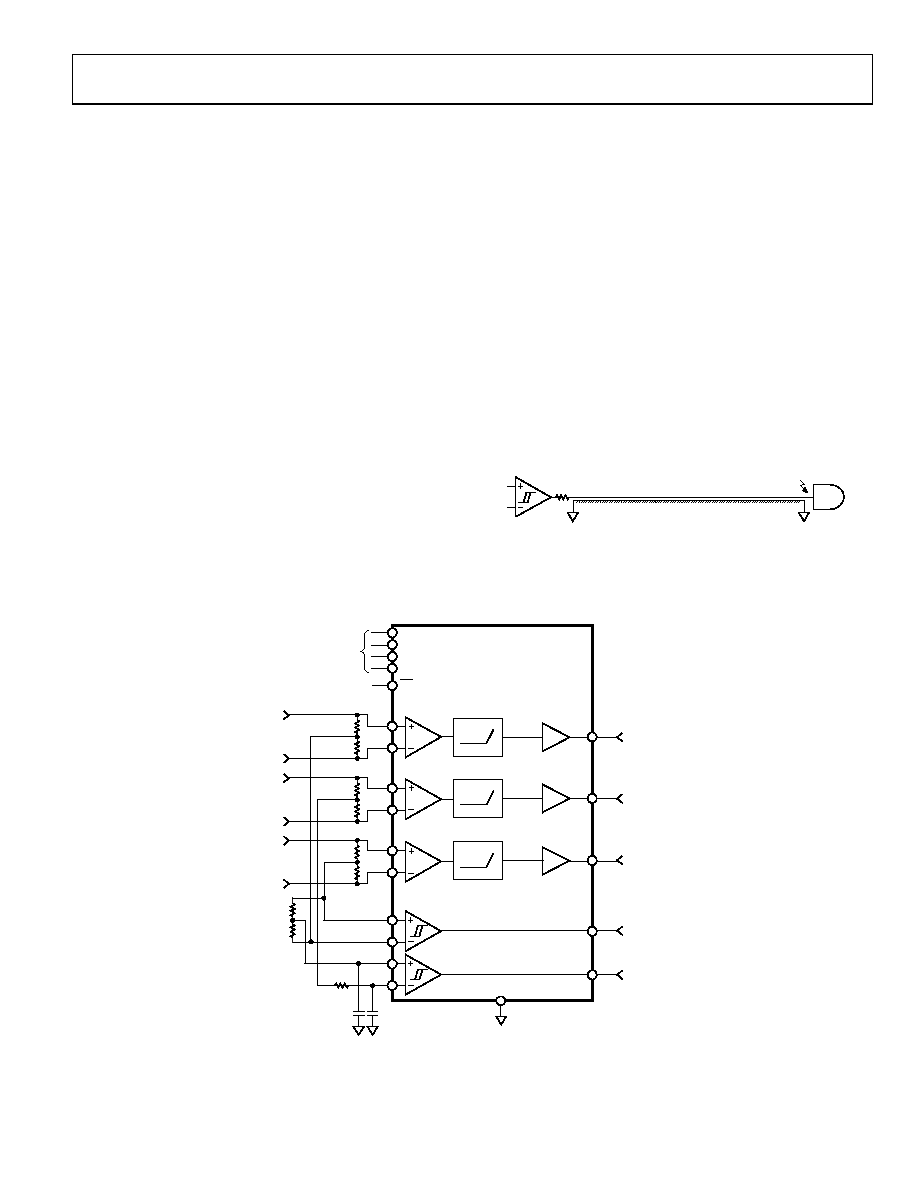

Figure 19 shows how to apply the comparators with source

termination when driving a 50 Ω transmission line that is high

impedance at its receive end.

06

81

4-

02

1

49.9

HIGH-Z

Z0 = 50

Figure 19. Using Comparator with Source Termination

18

RED

BLUE

GREEN

CMV

RED CMV

BLUE CMV

AD8123

15

12

6

4

VPEAK

26

25

27

23

28

VPOLE

VOFFSET

VGAIN

06

81

4-

0

20

HSYNC OUT

VSYNC OUT

32

31

GREEN

35

34

38

37

3

2

7

8

RECEIVED

RED VIDEO

RECEIVED

GREEN VIDEO

RECEIVED

BLUE VIDEO

RED VIDEO OUT

GREEN VIDEO OUT

BLUE VIDEO OUT

ANALOG

CONTROL

INPUTS

POWER DOWN

CONTROL

GND REFERENCE

24, 39

PD

1

2

1k

49.9

475

49.9

47pF

Figure 20. Basic Application Circuit with Common-Mode Sync Extraction

相关PDF资料 |

PDF描述 |

|---|---|

| AD5384BBC-3 | IC DAC 14BIT 40CH 3V 100-CSPBGA |

| AD5384BBC-3REEL7 | IC DAC 14BIT 40CH 3V 100-CSPBGA |

| ADCMP572BCPZ-R2 | IC COMPARATOR CML 3.3-5V 16LFCSP |

| LTC1687IS#PBF | IC TXRX RS485 PREC DELAY 14-SOIC |

| LTC1686IS8#PBF | IC TXRX RS485 PREC DELAY 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD8123ACPZ-R71 | 制造商:AD 制造商全称:Analog Devices 功能描述:Triple Differential Receiver with Adjustable Line Equalization |

| AD8123ACPZ-RL | 功能描述:IC RCVR TRPL DIFF EQUAL 40LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| AD8123ACPZ-RL1 | 制造商:AD 制造商全称:Analog Devices 功能描述:Triple Differential Receiver with Adjustable Line Equalization |

| AD8123ACPZ-TR | 制造商:Analog Devices 功能描述:TRIPLE EQUALIZER - Tape and Reel |

| AD8124 | 制造商:AD 制造商全称:Analog Devices 功能描述:Triple Differential Receiver with 200 Meter Adjustable Cable Equalization |

发布紧急采购,3分钟左右您将得到回复。