- 您现在的位置:买卖IC网 > PDF目录373939 > AD8150 (Analog Devices, Inc.) 33 x 17, 1.5 Gbps Digital Crosspoint Switch PDF资料下载

参数资料

| 型号: | AD8150 |

| 厂商: | Analog Devices, Inc. |

| 英文描述: | 33 x 17, 1.5 Gbps Digital Crosspoint Switch |

| 中文描述: | 33 × 17,1.5 Gbps的数字交叉点开关 |

| 文件页数: | 16/35页 |

| 文件大小: | 995K |

| 代理商: | AD8150 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

AD8150

–16–

REV. 0

UPDATE

7

0

1

2

16

33

1 OF 33

DECODERS

1 OF 17 DECODERS

WE

D[0:6]

RE

A[0:4]

RANK 1

17 RLATCHES

RANK 2

RESET

SWITCH

MATRIX

7

33

7

33

7

33

7

7

7

7

0

1

2

16

7

7

7

7

7

7

7

7

7

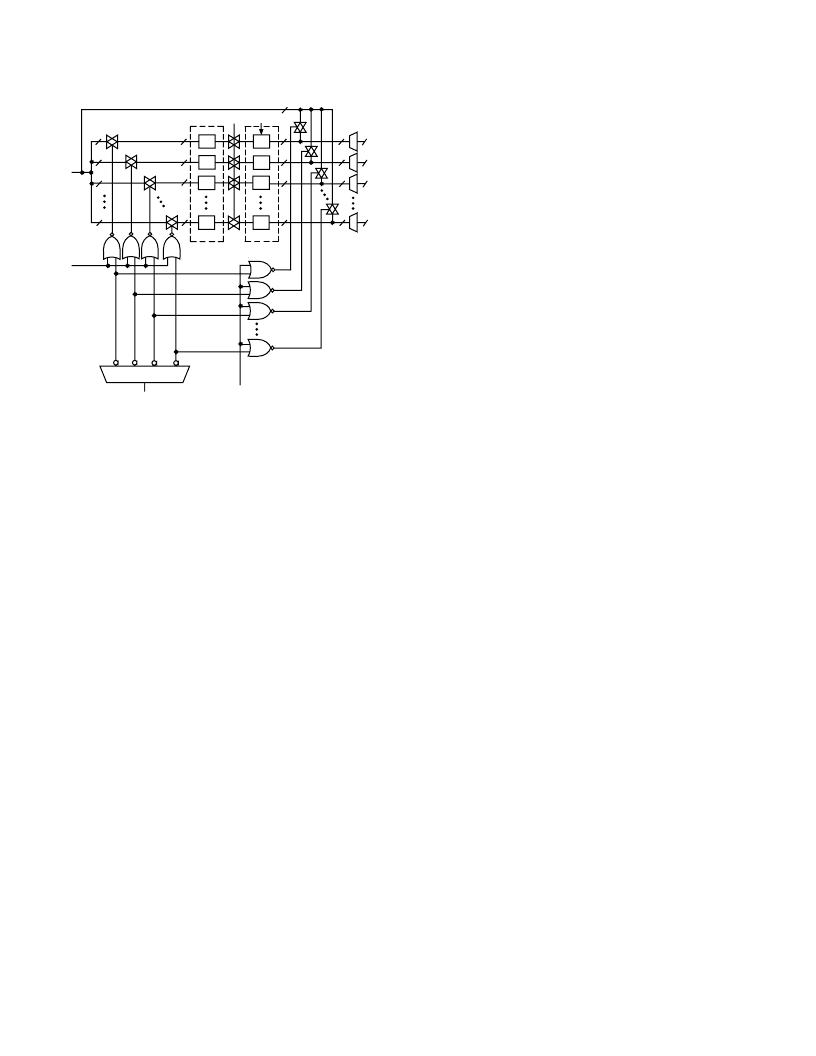

Figure 30. Control Interface (Simplified Schematic)

AD8150 CONTROL INTERFACE

The AD8150 control interface receives and stores the desired

connection matrix for the 33 input and 17 output signal pairs.

The interface consists of 17 rows of double-rank 7-bit latches,

one row for each output. The 7-bit data word stored in each

of these latches indicates to which (if any) of the 33 inputs the

output will be connected.

One output at a time can be preprogrammed by addressing the

output and writing the desired connection data into the first

rank of latches. This process can be repeated until each of the

desired output changes has been preprogrammed. All output

connections can then be programmed at once by passing the

data from the first rank of latches into the second rank. The out-

put connections always reflect the data programmed into the

second rank of latches, and do not change until the first rank of

data is passed into the second rank.

If necessary for system verification, the data in the second rank

of latches can be read back from the control interface.

At any time, a reset pulse can be applied to the control interface

to globally reset the appropriate second rank data bits, disabling

all 17 signal output pairs. This feature can be used to avoid out-

put bus contention on system start-up. The contents of the first

rank remain unchanged.

The control interface pins are connected via logic-level transla-

tors. These translators allow programming and readback of the

control interface using logic levels different from those in the

signal matrix.

In order to facilitate multiple chip address decoding, there is a

chip-select pin. All logic signals except the reset pulse are ignored

unless the chip select pin is active. The chip select pin disables

only the control logic interface, and does not change the opera-

tion of the signal matrix. The chip select pin does not power

down any of the latches, so any data programmed in the latches

is preserved.

All control pins are level-sensitive, not edge-triggered.

CONTROL PIN DESCRIPTION

A[4:0] Inputs

Output address pins. The binary encoded address applied to

these five input pins determines which one of the seventeen

outputs is being programmed (or being read back). The most

significant bit is A4.

D[6:0] Inputs/Outputs

Input configuration data pins. In write mode, the binary encoded

data applied to pins D[6:0] determine which one of 33 inputs is

to be connected to the output specified with the A[4:0] pins.

The most significant bit is D5, and the least significant bit is

D0. Bit D6 is the enable bit, setting the specified output sig-

nal pair to an enabled state if D6 is logic HIGH, or disabled

to a high-impedance state if D6 is logic LOW.

In readback mode, pins D[6:0] are low-impedance outputs indi-

cating the data word stored in the second rank for the output

specified with the A[4:0] pins. The readback drivers were designed

to drive high impedances only, so external drivers connected

to the D[6:0] should be disabled during readback mode.

WE

Input

First Rank Write Enable. Forcing this pin to logic LOW allows

the data on pins D[6:0] to be stored in the first rank latch for

the output specified by pins A[4:0]. The

WE

pin must be returned

to a logic HIGH state after a write cycle to avoid overwriting

the first rank data.

UPDATE

Input

Second Rank Write Enable. Forcing this pin to logic LOW allows

the data stored in all 17 first rank latches to be transferred to the

second rank latches. The signal connection matrix will be repro-

grammed when the second rank data is changed. This is a global

pin, transferring all 17 rows of data at once. It is not necessary

to program the address pins. It should be noted that after initial

power-up of the device, the first rank data is undefined. It may

be desirable to preprogram all seventeen outputs before performing

the first update cycle.

RE

Input

Second Rank Read-Enable. Forcing this pin to logic LOW enables

the output drivers on the bidirectional D[6:0] pins, entering the

readback mode of operation. By selecting an output address with

the A[4:0] pins and forcing

RE

to logic LOW, the 7-bit data

stored in the second rank latch for that output address will be

written to D[6:0] pins. Data should not be written to the D[6:0]

pins externally while in readback mode. The

RE

and

WE

pins

are not exclusive, and may be used at the same time, but data

should not be written to the D[6:0] pins from external sources

while in readback mode.

CS

Input

Chip-Select. This pin must be forced to logic LOW in order

to program or receive data from the logic interface, with the

exception of the

RESET

pin, described below. This pin has

no effect on the signal pairs and does not alter any of the stored

control data.

RESET

Input

Global Output Disable Pin. Forcing the

RESET

pin to logic

LOW will reset the enable bit, D6, in all 17 second rank

latches, regardless of the state of any other pins. This has the

effect of immediately disabling the 17 output signal pairs in the

相关PDF资料 |

PDF描述 |

|---|---|

| AD8150AST | 33 x 17, 1.5 Gbps Digital Crosspoint Switch |

| AD8151-EVAL | GPA/SK 300X280X1,5... |

| AD8151 | 33 x 17, 3.2 Gb/s Digital Crosspoint Switch |

| AD8151AST | 33 x 17, 3.2 Gb/s Digital Crosspoint Switch |

| AD8156 | 6.25 Gbps 4】4 Digital Crosspoint Switch with EQ |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD8150AST | 制造商:Rochester Electronics LLC 功能描述:LQFP 1.5GBPS 33X17 DIGITAL CROSSPOINT SW - Tape and Reel 制造商:Analog Devices 功能描述:IC SWITCH CROSSPOINT |

| AD8150ASTZ | 功能描述:IC CROSSPOINT SWIT 33X17 184LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 模拟开关,多路复用器,多路分解器 系列:XStream™ 应用说明:Ultrasound Imaging Systems Application Note 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:250 系列:- 功能:开关 电路:单刀单掷 导通状态电阻:48 欧姆 电压电源:单电源 电压 - 电源,单路/双路(±):2.7 V ~ 5.5 V 电流 - 电源:5µA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-LQFP 供应商设备封装:48-LQFP(7x7) 包装:托盘 |

| AD8150ASTZ | 制造商:Analog Devices 功能描述:IC DIGITAL CROSSPOINT SWITCH |

| AD8150-EVAL | 制造商:Analog Devices 功能描述:EVAL KIT FOR 33 17, 1.5 GBPS DGTL CROSSPOINT SWIT - Bulk |

| AD8151 | 制造商:AD 制造商全称:Analog Devices 功能描述:33 x 17, 3.2 Gb/s Digital Crosspoint Switch |

发布紧急采购,3分钟左右您将得到回复。