- 您现在的位置:买卖IC网 > PDF目录11209 > AD8155ACPZ-R7 (Analog Devices Inc)IC MUX/DEMUX DUAL BUFFER 64LFCSP PDF资料下载

参数资料

| 型号: | AD8155ACPZ-R7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 21/36页 |

| 文件大小: | 0K |

| 描述: | IC MUX/DEMUX DUAL BUFFER 64LFCSP |

| 标准包装: | 750 |

| 系列: | XStream™ |

| 功能: | 多路复用器/多路分解器 |

| 电路: | 2 x 2:1 |

| 电压电源: | 单电源 |

| 电压 - 电源,单路/双路(±): | 1.6 V ~ 3.6 V |

| 电流 - 电源: | 735mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页当前第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

AD8155

Rev. 0 | Page 28 of 36

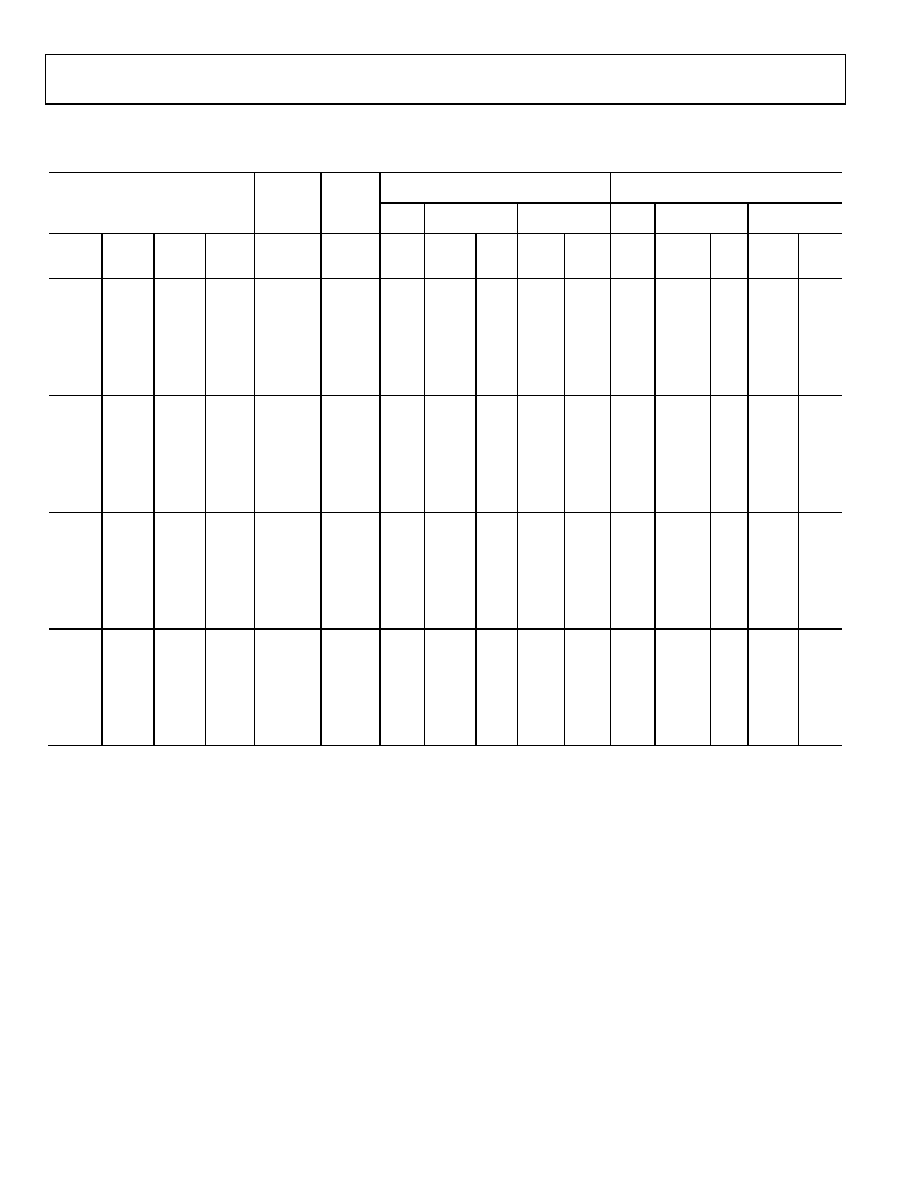

SIGNAL LEVELS AND COMMON-MODE SHIFT FOR AC-COUPLED AND DC-COUPLED OUTPUTS

Table 19. Output Voltage Range and Output Common-Mode Shift vs. Output Level and PE Setting

Output Levels and PE Boost

Register

Setting

Output

Current

AC-Coupled Transmitter

DC-Coupled Transmitter

VCC = VTTO = 3.3 V VCC = VTTO = 1.8 V

(mV)

VSW-PE1

(mV)

PE

Boost

(%)

PE (dB)

TX[A/B/C]

Level/PE

ITTO1 (mA)

ΔVOCM1

(mV)

VH-PE1

(V)

VL-PE1

(V)

VH-PE1

(V)

VL-PE1

(V)

ΔVOCM1

(mV)

VH-PE1

(V)

VL-PE1

(V)

VH-PE1

(V)

VL-PE1

(V)

200

0.00

0x00

8

200

3.2

3

1.7

1.5

100

3.3

3.1

1.8

1.6

200

300

50.00

3.52

0x01

12

300

3.15

2.85

1.65

1.35

150

3.3

3

1.8

1.5

200

400

100.00

6.02

0x02

16

400

3.1

2.7

1.6

1.2

200

3.3

2.9

1.8

1.4

200

500

150.00

7.96

0x03

20

500

3.05

2.55

1.55

1.05

250

3.3

2.8

1.8

1.3

200

600

200.00

9.54

0x04

24

600

3

2.4

1.5

0.9

300

3.3

2.7

1.8

1.2

200

700

250.00

10.88

0x05

28

700

2.95

2.25

1.45

0.75

350

3.3

2.6

1.8

1.1

200

800

300.00

12.04

0x06

32

800

2.9

2.1

1.4

0.6

400

3.3

2.5

1.8

1

300

0.00

0x10

12

300

3.15

2.85

1.65

1.35

150

3.3

3

1.8

1.5

300

400

33.33

2.50

0x11

16

400

3.1

2.7

1.6

1.2

200

3.3

2.9

1.8

1.4

300

500

66.67

4.44

0x12

20

500

3.05

2.55

1.55

1.05

250

3.3

2.8

1.8

1.3

300

600

100.00

6.02

0x13

24

600

3

2.4

1.5

0.9

300

3.3

2.7

1.8

1.2

300

700

133.33

7.36

0x14

28

700

2.95

2.25

1.45

0.75

350

3.3

2.6

1.8

1.1

300

800

166.67

8.52

0x15

32

800

2.9

2.1

1.4

0.6

400

3.3

2.5

1.8

1

300

900

200.00

9.54

0x16

36

900

2.85

1.95

1.35

0.45

450

3.3

2.4

1.8

0.9

400

0.00

0x20

16

400

3.1

2.7

1.6

1.2

200

3.3

2.9

1.8

1.4

400

500

25.00

1.94

0x21

20

500

3.05

2.55

1.55

1.05

250

3.3

2.8

1.8

1.3

400

600

50.00

3.52

0x22

24

600

3

2.4

1.5

0.9

300

3.3

2.7

1.8

1.2

400

700

75.00

4.86

0x23

28

700

2.95

2.25

1.45

0.75

350

3.3

2.6

1.8

1.1

400

800

100.00

6.02

0x24

32

800

2.9

1.4

0.6

400

3.3

2.5

1.8

1

400

900

125.00

7.04

0x25

36

900

2.85

1.35

0.45

450

3.3

2.4

1.8

0.9

400

1000

150.00

7.96

0x26

40

1000

2.8

1.84

1.3

0.3

500

3.3

2.3

1.8

0.8

600

0.00

0x30

24

600

3

2.4

1.5

0.9

300

3.3

2.7

1.8

1.2

600

700

16.67

1.34

0x31

28

700

2.95

2.25

1.45

0.75

350

3.3

2.6

1.8

1.1

600

800

33.33

2.50

0x32

32

800

2.9

2.13

1.4

0.65

400

3.3

2.5

1.8

1

600

900

50.00

3.52

0x33

36

900

2.85

1.954

1.35

0.454

450

3.3

2.4

1.8

0.9

600

1000

66.67

4.44

0x34

40

1000

2.8

1.84

1.3

0.34

500

3.3

2.3

1.8

0.8

600

1100

83.33

5.26

0x35

44

1100

2.75

1.654

1.25

0.154

550

3.3

2.2

1.8

0.7

600

1200

100.00

6.02

0x36

48

1200

2.7

1.54

1.2

600

3.3

2.13

1.8

1 Symbol definitions are shown in Table 20.

2 TX[A/B/C] level/PE control registers are port level control registers at Address 0x49, Address 0x89, and Address 0xC9. Per-lane level and PE control are in separate

registers.

3 This setting requires TX_HEADROOM = 1 to ensure adequate output compliance.

4 This setting is not recommended for ac-coupled outputs because the theoretical output low level is below the minimum output voltage limit listed in Table 1.

5 This setting is not recommended because the output level is below the minimum output voltage limit listed in Table 1. Use VCC = 2.5 V and TX_HEADROOM = 1.

相关PDF资料 |

PDF描述 |

|---|---|

| AD7512DIKP | IC SWITCH DUAL SPDT 20PLCC |

| ADG526AKR | IC MULTIPLEXER 16X1 28SOIC |

| ADG506AKNZ | IC MULTIPLEXER 16X1 28DIP |

| ADG506AKN | IC MULTIPLEXER 16X1 28DIP |

| SY55859LMG TR | IC CROSSPOINT SWITCH DUAL 32MLF |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD8155-EVALZ | 制造商:AD 制造商全称:Analog Devices 功能描述:6.5 Gbps Dual Buffer Mux/Demux |

| AD8155XCPZ | 制造商:Analog Devices 功能描述: |

| AD8156 | 制造商:AD 制造商全称:Analog Devices 功能描述:6.25 Gbps 4】4 Digital Crosspoint Switch with EQ |

| AD8156ABCZ | 功能描述:IC SWITCH XPT 4X4 W/EQ 49CSPBGA RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:XStream™ 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

| AD8156-EVALZ | 制造商:AD 制造商全称:Analog Devices 功能描述:6.25 Gbps 4】4 Digital Crosspoint Switch with EQ |

发布紧急采购,3分钟左右您将得到回复。