参数资料

| 型号: | AD8304ARU |

| 厂商: | Analog Devices Inc |

| 文件页数: | 8/20页 |

| 文件大小: | 0K |

| 描述: | IC LOGARITHM CONV 160DB 14-TSSOP |

| 设计资源: | Interfacing ADL5315 to Translinear Logarithmic Amplifier (CN0056) Interfacing ADL5317 High Side Current Mirror to a Translinear Logarithmic Amplifier in an Avalanche Photodiode Power Detector |

| 标准包装: | 1 |

| 类型: | 对数转换器 |

| 应用: | 光纤 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 14-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 14-TSSOP |

| 包装: | 管件 |

REV. A

–16–

AD8304

6

3

4

PDB

BIAS

VREF

10

2

12

VPDB

VSUM

INPT

VSUM

5

1

VNEG

~10k

ACOM

14

VPS2

PWDN

VPS1

VREF

7

VLOG

8

BFIN

9

BFNG

TEMPERATURE

COMPENSATION

5k

11

VOUT

0.5V

IPD

NC

R1

750

C1

1nF

13

VP

NC = NO CONNECT

RB

VOUT

VN (–0.5V TO –3V)

10nF

VOFS

AD8304

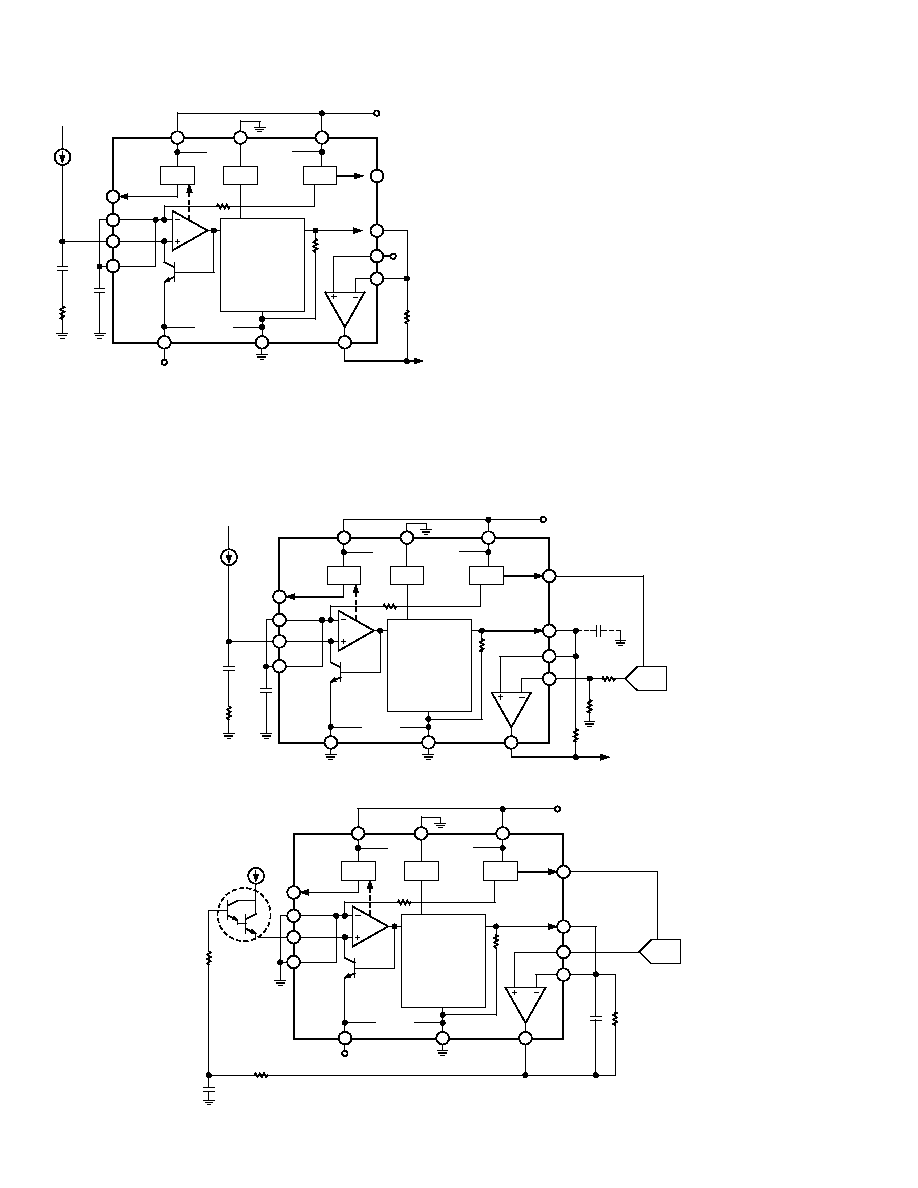

Figure 15. Using the Buffer to Invert the Polarity

of the Slope

When the gain is set to 13 (RB = 5 k

) the 2 V VREF can be tied

directly to BFIN, in which case the starting point for the output

response is at 4 V. However, since the slope in this case is only

–0.2 V/decade, the full current range will only take the output

down by 1.6 V. Clearly, a higher slope (or gain) is desirable, in

which case VOFS should be set to a smaller voltage to avoid railing

the output at low currents. If VOFS = 1.2 V and G = 33, VOUT

now starts at 4.8 V and falls through this same voltage toward

ground with a slope of –0.6 V per decade, spanning the full

range of IPD.

Programmable Level Comparator with Hysteresis

The buffer amplifier and reference voltage permit a calibrated

level detector to be realized. Figure 16 shows the use of a 10-bit

MDAC to control the setpoint to within 0.1 dB of an exact value

over the 100 dB range of 1 nA

≤ I

PD

≤ 100 A when the full-

scale output of the MDAC is equal to that of its reference. The

2 V VREF also sets the minimum value of VSPT to 0.2 V, correspond-

ing to an input of 1 nA. Since 100 dB at the VLOG interface

corresponds to a 1 V span, the resistor network is calculated to

provide a maximum VSPT of 1.2 V while adding the required

10% of VREF.

In this example, the hysteresis range is arranged to be 0.1 dB,

(1 mV at VLOG) when using a 5 V supply. This will usually be

adequate to prevent noise that causes the comparator output to

thrash. That risk can be reduced further by using a low-pass filtering

capacitor at VLOG (shown dotted) to decrease the noise bandwidth.

6

3

4

PDB

BIAS

VREF

10

2

12

VPDB

VSUM

INPT

VSUM

5

1

VNEG

~10k

ACOM

14

VPS2

PWDN

VPS1

VREF

7

VLOG

8

BFIN

9

BFNG

TEMPERATURE

COMPENSATION

5k

11

VOUT

0.5V

IPD

NC

750

1nF

13

VP

NC = NO CONNECT

50M

VOUT

10nF

VSPT

VREF

VOUT

MDAC

49.9k

100k

RH

AD8304

Figure 16. Calibrated Level Comparator

6

3

4

PDB

BIAS

VREF

10

2

12

VPDB

VSUM

INPT

VSUM

5

1

VNEG

~10k

ACOM

14

VPS2

PWDN

VPS1

VREF

7

VLOG

8

BFIN

9

BFNG

TEMPERATURE

COMPENSATION

5k

11

VOUT

0.5V

ISRC

25k

NC

13

VP

NC = NO CONNECT

C2

1nF

VN (–0.5V TO –5V)

1k

VREF

VOUT

MDAC

C1

10nF

100k

AD8304

Figure 17. Multidecade Current Source

相关PDF资料 |

PDF描述 |

|---|---|

| AD8305ACPZ-R2 | IC AMP LOG CONV 100DB 16-LFCSP |

| AD8306AR | IC LOGARITHM AMP 5-400MHZ 16SOIC |

| AD8307AN | IC LOGARITHMIC AMP 8-DIP |

| AD8309ARU | IC LOGARITHM AMP 100DB 16-TSSOP |

| AD830ANZ | IC VIDEO DIFF AMP HS 8-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD8304ARU-REEL | 制造商:Analog Devices 功能描述:SP Amp LOG Amp Single R-R O/P 5.5V 14-Pin TSSOP T/R 制造商:Analog Devices 功能描述:SP AMP LOG AMP SGL R-R O/P 5.5V 14TSSOP - Tape and Reel |

| AD8304ARU-REEL7 | 功能描述:IC LOGARITHMIC CONV 14-TSSOP T/R RoHS:否 类别:集成电路 (IC) >> 线性 - 放大器 - 专用 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:60 系列:- 类型:可变增益放大器 应用:CATV 安装类型:表面贴装 封装/外壳:20-WQFN 裸露焊盘 供应商设备封装:20-TQFN-EP(5x5) 包装:托盘 |

| AD8304ARUZ | 功能描述:IC LOGARITHM CONV 160DB 14-TSSOP RoHS:是 类别:集成电路 (IC) >> 线性 - 放大器 - 专用 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:60 系列:- 类型:可变增益放大器 应用:CATV 安装类型:表面贴装 封装/外壳:20-WQFN 裸露焊盘 供应商设备封装:20-TQFN-EP(5x5) 包装:托盘 |

| AD8304ARUZ | 制造商:Analog Devices 功能描述:Logarithmic Amplifier IC |

| AD8304ARUZ-RL7 | 功能描述:IC LOGARITHM CONV 160DB 14-TSSOP RoHS:是 类别:集成电路 (IC) >> 线性 - 放大器 - 专用 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:60 系列:- 类型:可变增益放大器 应用:CATV 安装类型:表面贴装 封装/外壳:20-WQFN 裸露焊盘 供应商设备封装:20-TQFN-EP(5x5) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。