- 您现在的位置:买卖IC网 > PDF目录97841 > AD8343ARUZ-REEL7 (ANALOG DEVICES INC) 0 MHz - 2500 MHz RF/MICROWAVE DOUBLE BALANCED MIXER PDF资料下载

参数资料

| 型号: | AD8343ARUZ-REEL7 |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | 混频器 |

| 英文描述: | 0 MHz - 2500 MHz RF/MICROWAVE DOUBLE BALANCED MIXER |

| 封装: | LEAD FREE, PLASTIC, TSSOP-14 |

| 文件页数: | 13/32页 |

| 文件大小: | 2171K |

| 代理商: | AD8343ARUZ-REEL7 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

AD8343

Rev. B | Page 20 of 32

OUTPUT INTERFACE (OUTP, OUTM)

The output of the AD8343 comprises a balanced pair of open

collector outputs. These should be biased to about the same

voltage as is connected to VPOS. Connecting them to an appre-

ciably higher voltage is likely to result in conduction of the ESD

protection network on signal peaks, causing high distortion levels.

On the other hand, setting the dc level of the outputs too low is

also likely to result in poor device linearity due to collector-base

capacitance modulation or saturation of the mixer core transistors.

OUTPUT MATCHING CONSIDERATIONS

The AD8343 requires a differential load for much the same

reasons that the input needs a differential source to achieve

optimal device performance. In addition, a differential load

provides the best LO to output isolation and the best input to

output isolation.

At low output frequencies, it is usually not appropriate to

arrange a conjugate match between the device output and

the load, even though doing so maximizes the small signal

conversion gain. This is because the output impedance at low

frequencies is quite high (a high resistance in parallel with a

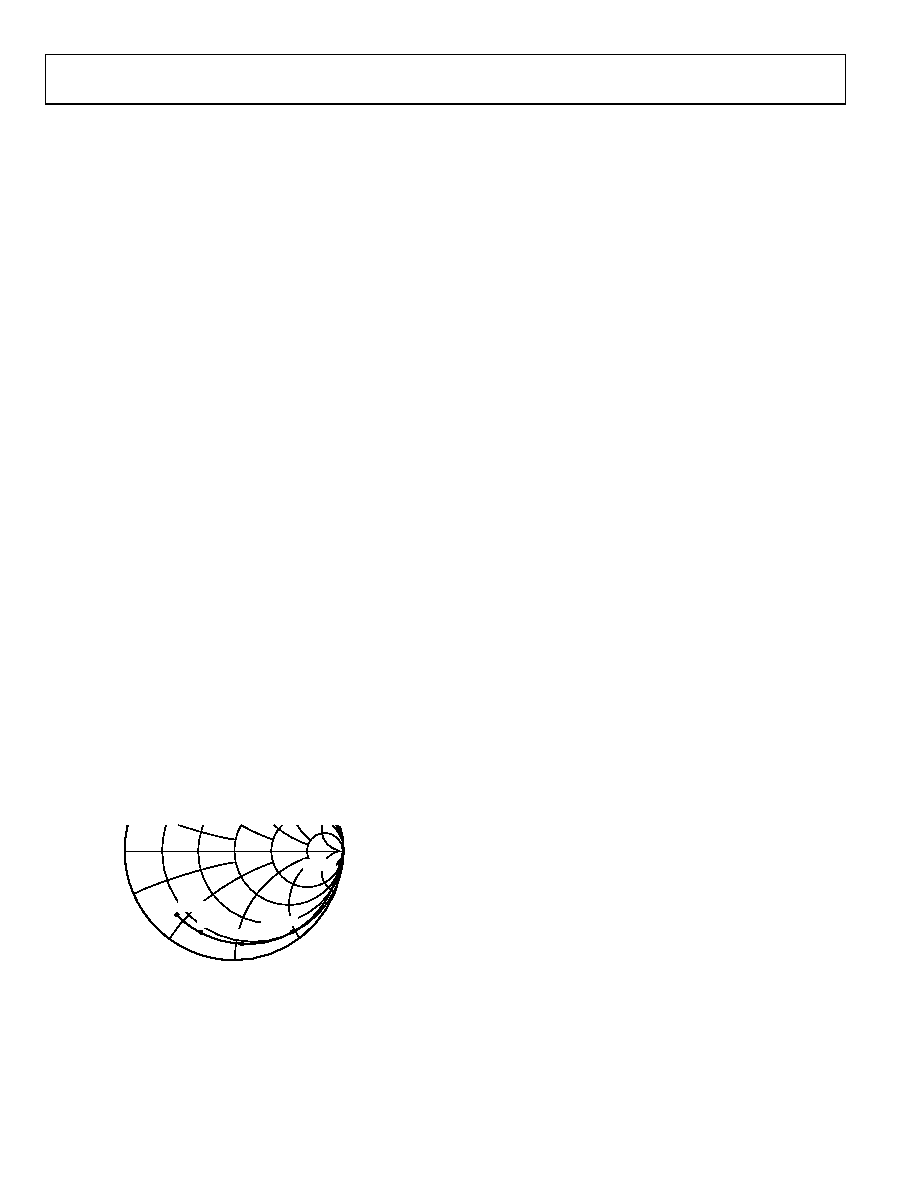

small capacitance). See Figure 60 for a plot of the differential

output impedance measured at the device pins. This data is

available in standard file format at the Analog Devices website

(http://www.analog.com); search for AD8343, then click on

AD8343 S-Parameters. If a matching high impedance load is

used, sufficient output voltage swing occurs to cause output

clipping even at relatively low input levels, constituting a loss

of dynamic range. The linear range of voltage swing at each

output pin is about ±1 V from the supply voltage VPOS. A

good compromise is to provide a load impedance of about

200 Ω to 500 Ω between the output pins at the desired output

frequency (based on 15 mA to 20 mA bias current at each

input). At output frequencies below 500 MHz, more output

power can be obtained before the onset of gross clipping by

using a lower load impedance; however, both gain and low

order distortion performance can be degraded.

500MHz

1000MHz

1500MHz

2000MHz

50MHz

FREQUENCY (50MHz TO 2500MHz)

01

03

4-

0

60

Figure 60. Output Differential Impedance (OUTP, OUTM)

The output load impedance must also be kept reasonably low

at the image frequency to avoid developing appreciable extra

voltage swing, which can reduce dynamic range.

If maintaining a good output return loss is not required, a 4:1 to

8:1 (impedance) flux-coupled transformer can be used to present a

suitable load to the device and to provide collector bias via a

center tap as shown in Figure 69. At all but the lowest output

frequencies, it becomes desirable to tune out the output capaci-

tance of the AD8343 by connecting an inductor between the

output pins. On the other hand, when a good output return loss

is desired, the output can be resistively loaded with a shunt

resistance between the output pins in order to set the real value

of output impedance. With selection of both the transformer’s

impedance ratio and the shunting resistance as required, the

desired total load (~500 Ω) is achieved while optimizing both

signal transfer and output return loss.

At higher output frequencies, the output conductance of the

device becomes higher (see Figure 60), with the consequence

that above about 900 MHz, it does become appropriate to

perform a conjugate match between the load and the AD8343s

output. The device’s own output admittance becomes sufficient

to remove the threat of clipping from excessive voltage swing.

Just as for the input, it is best to perform differential output

impedance measurements on the board layout to effectively

develop a good matching network.

OUTPUT BIASING CONSIDERATIONS

When the output single-ended-to-differential conversion takes

the form of a transformer whose primary winding is center

tapped, simply apply VPOS to the tap, preferably through a

ferrite bead in series with the tap in order to avoid a common

mode instability problem (see the Input and Output Stability

Considerations section). See Figure 69 for an example of this

network. The collector dc bias voltage must be nominally equal

to the supply voltage applied to Pin 5 (VPOS).

If a 1:1 transmission line balun is used for the output, it is

necessary to bring in collector bias through separate inductors.

These inductors are chosen to obtain a high impedance over

the RF output frequency range of interest. See Figure 70 for an

example of this network.

相关PDF资料 |

PDF描述 |

|---|---|

| AD8343ARUZ-REEL | 0 MHz - 2500 MHz RF/MICROWAVE DOUBLE BALANCED MIXER |

| AD8345AREZ1 | 140 MHz - 1000 MHz RF/MICROWAVE QUADRAPHASE MODULATOR |

| AD8345AREZ-RL7 | 140 MHz - 1000 MHz RF/MICROWAVE QUADRAPHASE MODULATOR |

| AD8345AREZ-REEL7 | 140 MHz - 1000 MHz RF/MICROWAVE QUADRAPHASE MODULATOR |

| AD8346ARUZ-REEL | 800 MHz - 2500 MHz RF/MICROWAVE I/Q MODULATOR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD8343-EVAL | 制造商:Analog Devices 功能描述:AD8343 EVALUATION BOARD - Bulk |

| AD8343-EVALZ | 制造商:Analog Devices 功能描述:AD8343 EVALUATION BOARD - Bulk |

| AD8344 | 制造商:AD 制造商全称:Analog Devices 功能描述:Active Receive Mixer 400 MHz to 1.2 GHz |

| AD8344ACPZ | 制造商:Analog Devices 功能描述:UP/DOWN CONV MIXER 5V 1.2GHZ 16LFCSP EP - Tape and Reel 制造商:Analog Devices 功能描述:IC SM RF MIXER 800MHZ |

| AD8344ACPZ | 制造商:Analog Devices 功能描述:IC RF MIXER 800MHZ SMD LFCSP-16 |

发布紧急采购,3分钟左右您将得到回复。