- 您现在的位置:买卖IC网 > PDF目录10677 > AD9201ARSZ (Analog Devices Inc)IC ADC CMOS 10BIT DUAL 28-SSOP PDF资料下载

参数资料

| 型号: | AD9201ARSZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 5/20页 |

| 文件大小: | 0K |

| 描述: | IC ADC CMOS 10BIT DUAL 28-SSOP |

| 标准包装: | 47 |

| 位数: | 10 |

| 采样率(每秒): | 20M |

| 数据接口: | 并联 |

| 转换器数目: | 2 |

| 功率耗散(最大): | 245mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 28-SSOP |

| 包装: | 管件 |

| 输入数目和类型: | 4 个单端,单极;2 个差分,单极 |

| 产品目录页面: | 780 (CN2011-ZH PDF) |

AD9201

–13–

REV. D

DIGITAL INPUTS AND OUTPUTS

Each of the AD9201 digital control inputs, CHIP SELECT,

CLOCK, SELECT and SLEEP are referenced to AVDD and

AVSS. Switching thresholds will be AVDD/2.

The format of the digital output is straight binary. A low power

mode feature is provided such that for STBY = HIGH and the

clock disabled, the static power of the AD9201 will drop below

22 mW.

CLOCK INPUT

The AD9201 clock input is internally buffered with an inverter

powered from the AVDD pin. This feature allows the AD9201

to accommodate either +5 V or +3.3 V CMOS logic input sig-

nal swings with the input threshold for the CLK pin nominally

at AVDD/2.

The pipelined architecture of the AD9201 operates on both

rising and falling edges of the input clock. To minimize duty

cycle variations the logic family recommended to drive the clock

input is high speed or advanced CMOS (HC/HCT, AC/ACT)

logic. CMOS logic provides both symmetrical voltage threshold

levels and sufficient rise and fall times to support 20 MSPS

operation. Running the part at slightly faster clock rates may be

possible, although at reduced performance levels. Conversely,

some slight performance improvements might be realized by

clocking the AD9201 at slower clock rates.

The power dissipated by the output buffers is largely propor-

tional to the clock frequency; running at reduced clock rates

provides a reduction in power consumption.

DIGITAL OUTPUTS

Each of the on-chip buffers for the AD9201 output bits (D0–D9)

is powered from the DVDD supply pin, separate from AVDD.

The output drivers are sized to handle a variety of logic families

while minimizing the amount of glitch energy generated. In all

cases, a fan-out of one is recommended to keep the capacitive

load on the output data bits below the specified 20 pF level.

For DVDD = 5 V, the AD9201 output signal swing is compat-

ible with both high speed CMOS and TTL logic families. For

TTL, the AD9201 on-chip, output drivers were designed to

support several of the high speed TTL families (F, AS, S). For

applications where the clock rate is below 20 MSPS, other TTL

families may be appropriate. For interfacing with lower voltage

CMOS logic, the AD9201 sustains 20 MSPS operation with

DVDD = 3 V. In all cases, check your logic family data sheets

for compatibility with the AD9201’s Specification table.

A 2 ns reduction in output delays can be achieved by limiting

the logic load to 5 pF per output line.

THREE-STATE OUTPUTS

The digital outputs of the AD9201 can be placed in a high

impedance state by setting the CHIP SELECT pin to HIGH.

This feature is provided to facilitate in-circuit testing or evaluation.

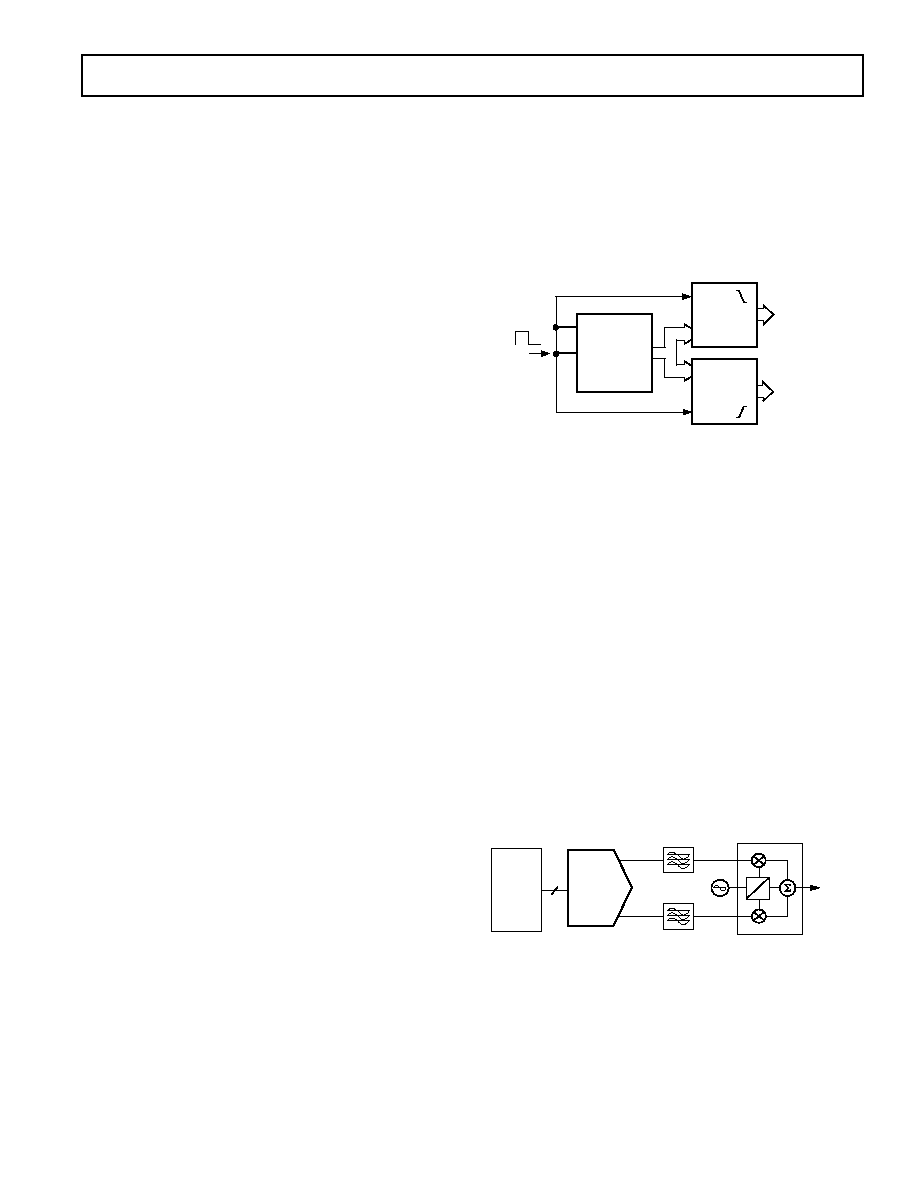

SELECT

When the select pin is held LOW, the output word will present

the “Q” level. When the select pin is held HIGH, the “I” level

will be presented to the output word (see Figure 1).

The AD9201’s select and clock pins may be driven by a com-

mon signal source. The data will change in 5 ns to 11 ns after

the edges of the input pulse. The user must make sure the inter-

face latches have sufficient hold time for the AD9201’s delays

(see Figure 30).

CLOCK

DATA

I LATCH

CLOCK

DATA

Q LATCH

CLK

DATA

OUT

SELECT

I

PROCESSING

Q

PROCESSING

CLOCK

SOURCE

Figure 30. Typical De-Mux Connection

APPLICATIONS

USING THE AD9201 FOR QAM DEMODULATION

QAM is one of the most widely used digital modulation schemes

in digital communication systems. This modulation technique

can be found in both FDMA as well as spread spectrum (i.e.,

CDMA) based systems. A QAM signal is a carrier frequency

which is both modulated in amplitude (i.e., AM modulation)

and in phase (i.e., PM modulation). At the transmitter, it can

be generated by independently modulating two carriers of iden-

tical frequency but with a 90

° phase difference. This results in

an inphase (I) carrier component and a quadrature (Q) carrier

component at a 90

° phase shift with respect to the I component.

The I and Q components are then summed to provide a QAM

signal at the specified carrier or IF frequency. Figure 31 shows

a typical analog implementation of a QAM modulator using a

dual 10-bit DAC with 2

× interpolation, the AD9761. A QAM

signal can also be synthesized in the digital domain thus requir-

ing a single DAC to reconstruct the QAM signal. The AD9853

is an example of a complete (i.e., DAC included) digital QAM

modulator.

0

90

DSP

OR

ASIC

10

CARRIER

FREQUENCY

NYQUIST

FILTERS

TO

MIXER

QUADRATURE

MODULATOR

AD9761

IOUT

QOUT

Figure 31. Typical Analog QAM Modulator Architecture

相关PDF资料 |

PDF描述 |

|---|---|

| AD7266BCPZ | IC ADC 12BIT 3CH 2MSPS 32-LFCSP |

| 1676860-5 | CAP CER 1PF 50V 5% NP0 1206 |

| AD1871YRSZ | IC ADC STEREO AUDIO 24BIT 28SSOP |

| 1676859-4 | CAP CER 0.82PF 200V 5% NP0 0805 |

| 1676859-3 | CAP CER 0.68PF 200V 5% NP0 0805 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9201ARSZRL | 功能描述:IC ADC 10BIT 2CH 40MSPS 28-SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| AD9201-EVAL | 制造商:Analog Devices 功能描述:DEV TOOLS, EVAL BD FOR DUAL CH, 20MHZ 10BIT RESOLUTION CMOS - Bulk 制造商:Analog Devices 功能描述:AD9201 EVAL BOARD |

| AD9201EVALBOARD | 制造商:AD 制造商全称:Analog Devices 功能描述:*AD9201 EVAL BOARD* |

| AD9202JRS | 制造商:Analog Devices 功能描述: |

| AD9202JRSRL | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 10-Bit |

发布紧急采购,3分钟左右您将得到回复。