- 您现在的位置:买卖IC网 > PDF目录10062 > AD9212ABCPZ-40 (Analog Devices Inc)IC ADC 10BIT SRL 40MSPS 64LFCSP PDF资料下载

参数资料

| 型号: | AD9212ABCPZ-40 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 16/56页 |

| 文件大小: | 0K |

| 描述: | IC ADC 10BIT SRL 40MSPS 64LFCSP |

| 标准包装: | 1 |

| 位数: | 10 |

| 采样率(每秒): | 40M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 8 |

| 功率耗散(最大): | 560mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 托盘 |

| 输入数目和类型: | 16 个单端,单极;8 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

Data Sheet

AD9212

Rev. E | Page 23 of 56

CLOCK INPUT CONSIDERATIONS

For optimum performance, the AD9212 sample clock inputs

(CLK+ and CLK) should be clocked with a differential signal.

This signal is typically ac-coupled into the CLK+ and CLK pins

via a transformer or capacitors. These pins are biased internally

and require no additional biasing.

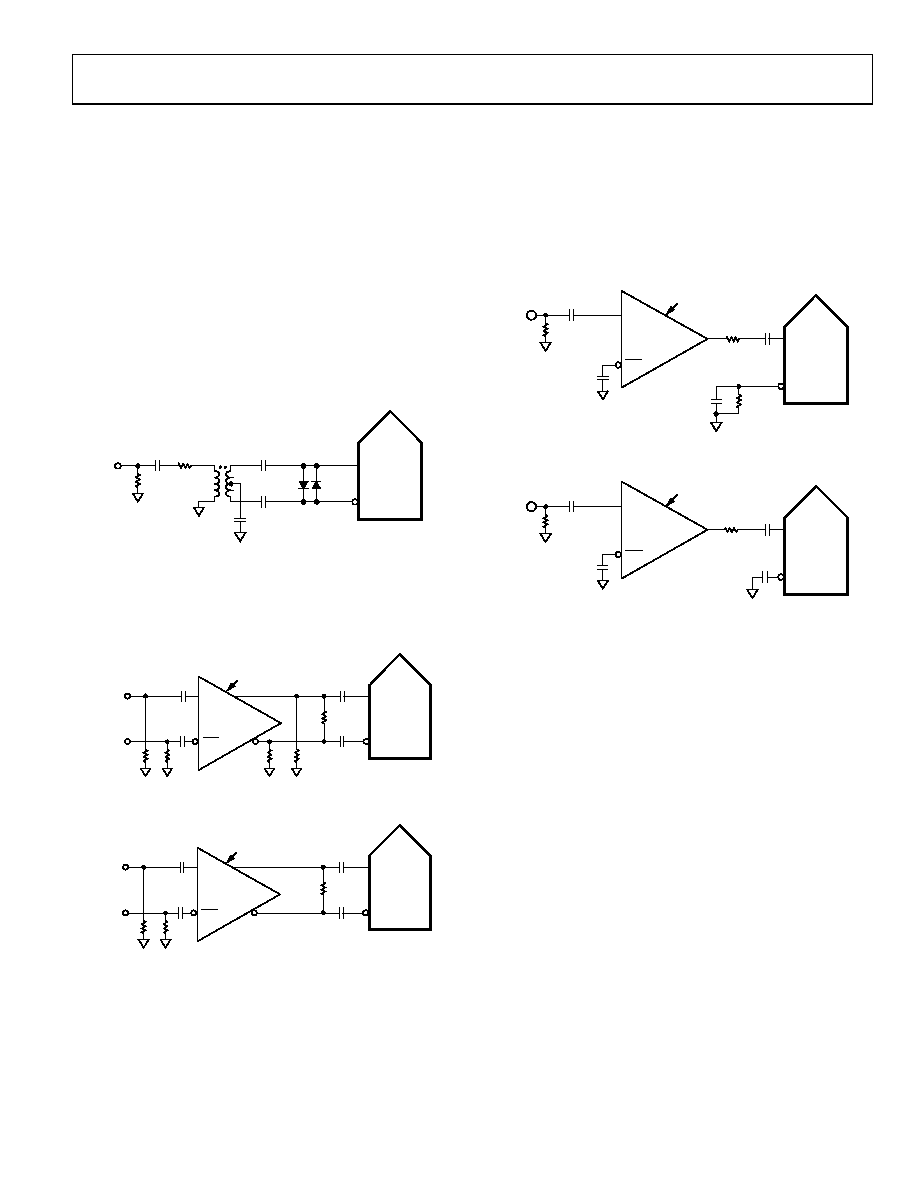

Figure 51 shows the preferred method for clocking the AD9212.

The low jitter clock source is converted from single-ended to

differential using an RF transformer. The back-to-back Schottky

diodes across the secondary transformer limit clock excursions

into the AD9212 to approximately 0.8 V p-p differential. This

helps prevent the large voltage swings of the clock from feeding

through to other portions of the AD9212, and it preserves the

fast rise and fall times of the signal, which are critical to low

jitter performance.

0.1F

SCHOTTKY

DIODES:

HSM2812

CLK+

50

100

CLK–

CLK+

ADC

AD9212

Mini-Circuits

ADT1–1WT, 1:1Z

XFMR

05

96

8-

02

2

Figure 51. Transformer-Coupled Differential Clock

Another option is to ac-couple a differential PECL signal to the

sample clock input pins as shown in Figure 52. The AD9510/

drivers offers excellent jitter performance.

100

0.1F

240

AD9510/AD9511/

AD9512/AD9513/

AD9514/AD9515

501

CLK

150 RESISTORS ARE OPTIONAL.

CLK–

CLK+

ADC

AD9212

PECL DRIVER

05968-

023

CLK+

CLK–

Figure 52. Differential PECL Sample Clock

100

0.1F

501

LVDS DRIVER

501

CLK

150 RESISTORS ARE OPTIONAL.

CLK–

CLK+

ADC

AD9212

AD9510/AD9511/

AD9512/AD9513/

AD9514/AD9515

059

68-

02

4

CLK+

CLK–

Figure 53. Differential LVDS Sample Clock

In some applications, it is acceptable to drive the sample clock

inputs with a single-ended CMOS signal. In such applications,

CLK+ should be driven directly from a CMOS gate, and the

CLK pin should be bypassed to ground with a 0.1 μF capacitor

in parallel with a 39 kΩ resistor (see Figure 54). Although the

CLK+ input circuit supply is AVDD (1.8 V), this input is

designed to withstand input voltages of up to 3.3 V, making the

selection of the drive logic voltage very flexible.

0.1F

39k

CMOS DRIVER

501

OPTIONAL

100

0.1F

CLK

150 RESISTOR IS OPTIONAL.

CLK–

CLK+

ADC

AD9212

AD9510/AD9511/

AD9512/AD9513/

AD9514/AD9515

05

96

8-

0

25

CLK+

Figure 54. Single-Ended 1.8 V CMOS Sample Clock

0.1F

CMOS DRIVER

501

OPTIONAL

100

CLK

150 RESISTOR IS OPTIONAL.

0.1F

CLK–

CLK+

ADC

AD9212

AD9510/AD9511/

AD9512/AD9513/

AD9514/AD9515

05

96

8-

02

6

CLK+

Figure 55. Single-Ended 3.3 V CMOS Sample Clock

Clock Duty Cycle Considerations

Typical high speed ADCs use both clock edges to generate a

variety of internal timing signals. As a result, these ADCs may

be sensitive to the clock duty cycle. Commonly, a 5% tolerance is

required on the clock duty cycle to maintain dynamic performance

characteristics. The AD9212 contains a duty cycle stabilizer (DCS)

that retimes the nonsampling edge, providing an internal clock

signal with a nominal 50% duty cycle. This allows a wide range

of clock input duty cycles without affecting the performance of

the AD9212. When the DCS is on, noise and distortion perfor-

mance are nearly flat for a wide range of duty cycles. However,

some applications may require the DCS function to be off. If so,

keep in mind that the dynamic range performance can be affected

when operated in this mode. See the Memory Map section for

more details on using this feature.

The duty cycle stabilizer uses a delay-locked loop (DLL) to

create the nonsampling edge. As a result, any changes to the

sampling frequency require approximately eight clock cycles

to allow the DLL to acquire and lock to the new rate.

相关PDF资料 |

PDF描述 |

|---|---|

| MS27466T23F53PD | CONN RCPT 53POS WALL MT W/PINS |

| AD7871JPZ-REEL | IC ADC 14BIT SAMPLING 28-PLCC |

| LTC2369HMS-18#TRPBF | IC ADC 18BIT SRL/SPI 16-MSOP |

| IDT7284L12PA8 | IC FIFO 2048X18 12NS 56TSSOP |

| D38999/24FC8SD | CONN RCPT 8POS JAM NUT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9212ABCPZ-65 | 功能描述:IC ADC 10BIT SRL 65MSPS 64LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD9212ABCPZRL7-40 | 功能描述:IC ADC 10BIT SRL 40MSPS 64LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD9212ABCPZRL7-65 | 功能描述:IC ADC 10BIT SRL 65MSPS 64LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD9212BCPZ-40 | 制造商:Analog Devices 功能描述:ADC Octal Pipelined 40Msps 10-bit Serial 64-Pin LFCSP EP 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述:IC 10BIT ADC 40/65MSPS 1.8V SMD 制造商:Analog Devices 功能描述:IC, 10BIT ADC, 40/65MSPS, 1.8V, SMD |

| AD9212BCPZ-65 | 制造商:Analog Devices 功能描述:ADC Octal Pipelined 65Msps 10-bit Serial 64-Pin LFCSP EP |

发布紧急采购,3分钟左右您将得到回复。