- 您现在的位置:买卖IC网 > PDF目录17025 > AD9267EBZ (Analog Devices Inc)BOARD EVALUATION FOR AD9267 PDF资料下载

参数资料

| 型号: | AD9267EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 8/24页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD9267 |

| 标准包装: | 1 |

| ADC 的数量: | 2 |

| 位数: | 16 |

| 采样率(每秒): | 640M |

| 数据接口: | 串行,SPI? |

| 输入范围: | 2 ~ 3 Vpp |

| 在以下条件下的电源(标准): | 416mW @ 640MSPS |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | AD9267 |

| 已供物品: | 板 |

AD9267

Rev. 0 | Page 16 of 24

The reference clock, CLK±, is limited to 30 MHz to 160 MHz

when configured to use the on-chip clock multiplier. Given the

input range of the reference clock and the available multiplica-

tion factors, the fVCO is approximately 1280 MHz. This results in

the desired fMOD rate of 640 MHz with a 50% duty cycle.

The PLL of the AD9267 can be controlled through either the serial

port interface or the PLLMULTx pins. For serial port interface

control, Register 0x09 and Register 0x0A are used. Before the

PLL enable register bit (PLLENABLE) is set, the PLL multiplica-

tion factor should be programmed into Register 0x0A[5:0].

After setting the PLLENABLE bit, the PLL locks and reports a

locked state in Register 0x0A[7]. If the PLL multiplication factor

is changed, the PLL enable bit should be reset and set again.

Some common clock multiplication factors are shown in Table 8.

The recommended sequence for enabling and programming the

on-chip clock multiplier is as follows:

1.

Apply a reference clock to the CLK± pins.

2.

Program the PLL multiplication factor in

Register 0x0A[5:0]. See Table 8.

3.

Enable the PLL; Register 0x09 = 04 (decimal).

External PLL Control

At power-up, the serial interface is disabled until the first serial

port access. If the serial interface is disabled, the PLLMULTx

pins control the PLL multiplication factor. The five PLLMULTx

pins (Pin 44 to Pin 48) offer all the available multiplication

factors. If all PLLMULTx pins are tied high, the PLL is disabled

and the AD9267 assumes the high frequency modulator clock

rate that is applied to the CLK± pins. Table 10 shows the relation-

ship between PLLMULTx pins and the PLL multiplication factor.

PLL Autoband Select

The PLL VCO has a wide operating range that is covered by

overlapping frequency bands. For any desired VCO output fre-

quency, there are multiple valid PLL band select values. The

AD9267 possesses an automatic PLL band select feature on chip

that determines the optimal PLL band setting. This feature can

be enabled by writing to Register 0x0A[6] and is the recom-

mended configuration with the PLL clocking option.

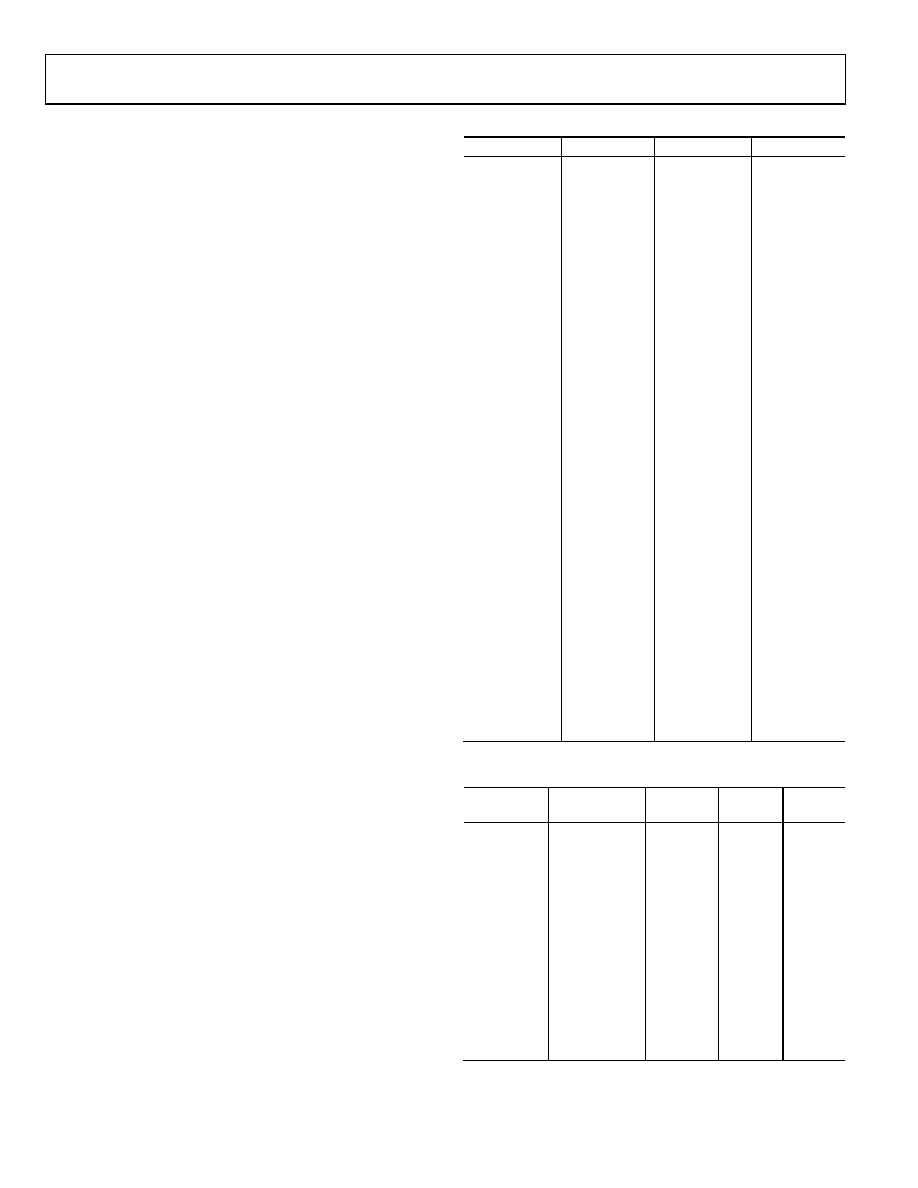

Table 8. PLL Multiplication Factors

0x0A[5:0]

PLLMULT (N)

0x0A[5:0]

PLLMULT (N)

1

8

33

32

2

8

34

3

8

35

34

4

8

36

34

5

8

37

34

6

8

38

34

7

8

39

34

8

40

34

9

41

34

10

42

11

10

43

42

12

44

42

13

12

45

42

14

46

42

15

47

42

16

48

42

17

49

42

18

50

42

19

18

51

42

20

52

42

21

53

42

22

21

54

42

23

21

55

42

24

56

42

25

57

42

26

25

58

42

27

25

59

42

28

60

42

29

28

61

42

30

62

42

31

30

63

42

32

64

42

Table 9. Common Modulator Clock Multiplication Factors

CLK±

(MHz)

0x0A[5:0]

(PLLMULT)

fVCO

(MHz)

fMOD

(MHz)

BW

(MHz)

30.72

42

1290.24

645.12

10.08

39.3216

32

1258.29

629.15

9.83

52.00

25

1300.00

650.00

10.16

61.44

21

1290.24

645.12

10.08

76.80

17

1305.60

652.80

10.20

78.00

17

1326.00

663.00

10.36

78.6432

16

1258.29

629.15

9.83

89.60

15

1344.00

672.00

10.50

92.16

14

1290.24

645.12

10.08

122.88

10

1228.80

614.40

9.60

134.40

10

1344.00

672.00

10.50

153.60

8

1228.80

614.40

9.60

157.2864

8

1258.29

629.15

9.83

相关PDF资料 |

PDF描述 |

|---|---|

| EBM18DRAI | CONN EDGECARD 36POS R/A .156 SLD |

| RBM18DRMD | CONN EDGECARD 36POS .156 WW |

| ECM30DCSN | CONN EDGECARD 60POS DIP .156 SLD |

| 0982660143 | CBL 14POS 0.5MM JMPR TYPE A 3" |

| ECM30DCSH | CONN EDGECARD 60POS DIP .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9268 | 制造商:AD 制造商全称:Analog Devices 功能描述:16-Bit, 80 MSPS/105 MSPS/125 MSPS, 1.8 V Dual Analog-to-Digital Converter (ADC) |

| AD9268-105EBZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:16-Bit, 80 MSPS/105 MSPS/125 MSPS, 1.8 V Dual Analog-to-Digital Converter (ADC) |

| AD9268-125EBZ | 功能描述:数据转换 IC 开发工具 Dual 16 bit 125 high SNR ADC RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| AD9268-125EBZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:16-Bit, 80 MSPS/105 MSPS/125 MSPS, 1.8 V Dual Analog-to-Digital Converter (ADC) |

| AD9268-80EBZ1 | 制造商:AD 制造商全称:Analog Devices 功能描述:16-Bit, 80 MSPS/105 MSPS/125 MSPS, 1.8 V Dual Analog-to-Digital Converter (ADC) |

发布紧急采购,3分钟左右您将得到回复。