- 您现在的位置:买卖IC网 > PDF目录1987 > AD9517-4ABCPZ-RL7 (Analog Devices Inc)IC CLOCK GEN 1.8GHZ VCO 48LFCSP PDF资料下载

参数资料

| 型号: | AD9517-4ABCPZ-RL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 5/80页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN 1.8GHZ VCO 48LFCSP |

| 设计资源: | High Performance, Dual Channel IF Sampling Receiver (CN0140) |

| 标准包装: | 750 |

| 类型: | 时钟发生器,扇出配送 |

| PLL: | 是 |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:12 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 1.8GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 48-LFCSP-VQ(7x7) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

Data Sheet

AD9517-4

Rev. E | Page 13 of 80

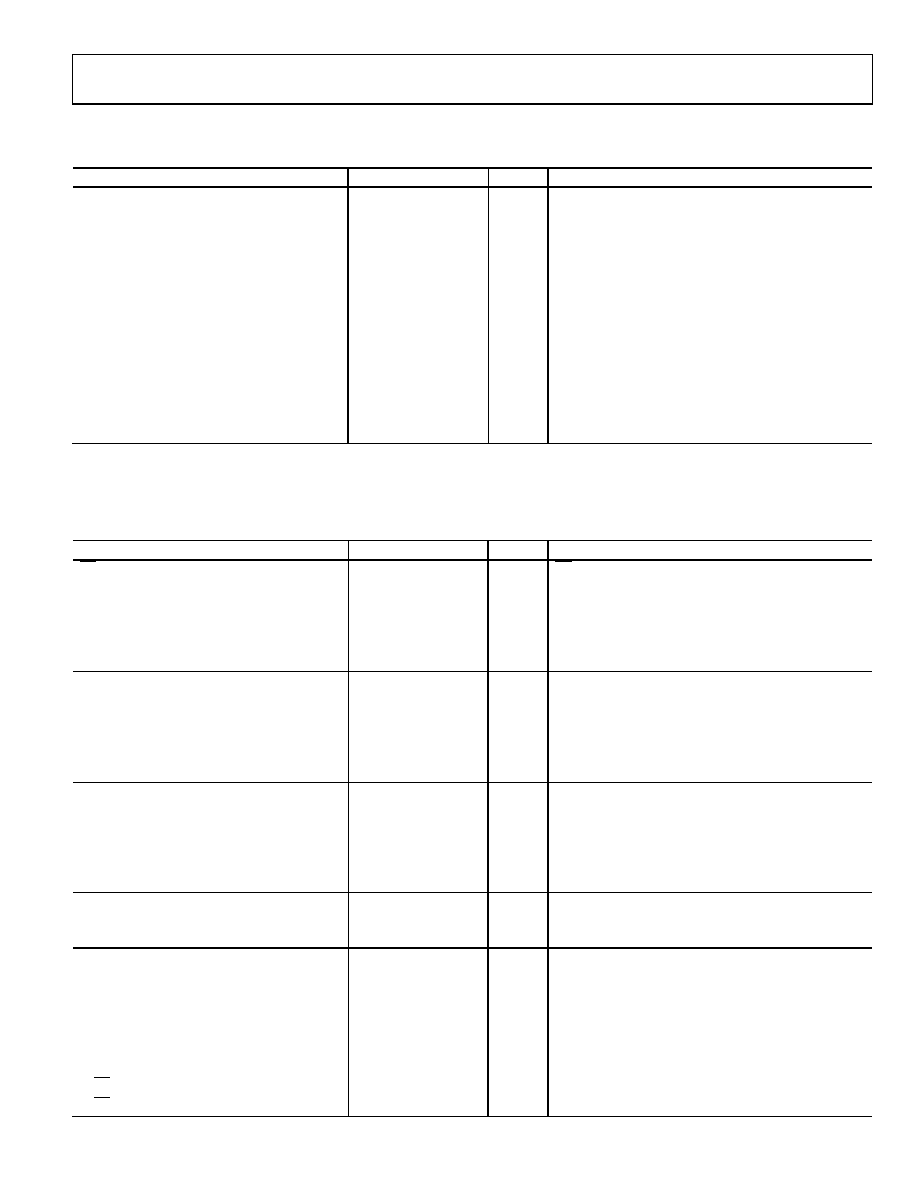

DELAY BLOCK ADDITIVE TIME JITTER

Table 13.

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

DELAY BLOCK ADDITIVE TIME JITTER1

Incremental additive jitter

100 MHz Output

Delay (1600 A, 0x1C) Fine Adj. 000000b

0.54

ps rms

Delay (1600 A, 0x1C) Fine Adj. 101111b

0.60

ps rms

Delay (800 A, 0x1C) Fine Adj. 000000b

0.65

ps rms

Delay (800 A, 0x1C) Fine Adj. 101111b

0.85

ps rms

Delay (800 A, 0x4C) Fine Adj. 000000b

0.79

ps rms

Delay (800 A, 0x4C) Fine Adj. 101111b

1.2

ps rms

Delay (400 A, 0x4C) Fine Adj. 000000b

1.2

ps rms

Delay (400 A, 0x4C) Fine Adj. 101111b

2.0

ps rms

Delay (200 A, 0x1C) Fine Adj. 000000b

1.3

ps rms

Delay (200 A, 0x1C) Fine Adj. 101111b

2.5

ps rms

Delay (200 A, 0x4C) Fine Adj. 000000b

1.9

ps rms

Delay (200 A, 0x4C) Fine Adj. 101111b

3.8

ps rms

1

This value is incremental. That is, it is in addition to the jitter of the LVDS or CMOS output without the delay. To estimate the total jitter, the LVDS or CMOS output jitter

should be added to this value using the root sum of the squares (RSS) method.

SERIAL CONTROL PORT

Table 14.

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

CS (INPUT)

CS has an internal 30 k pull-up resistor

Input Logic 1 Voltage

2.0

V

Input Logic 0 Voltage

0.8

V

Input Logic 1 Current

3

A

Input Logic 0 Current

110

A

Input Capacitance

2

pF

SCLK (INPUT)

SCLK has an internal 30 k pull-down resistor

Input Logic 1 Voltage

2.0

V

Input Logic 0 Voltage

0.8

V

Input Logic 1 Current

110

A

Input Logic 0 Current

1

A

Input Capacitance

2

pF

SDIO (WHEN INPUT)

Input Logic 1 Voltage

2.0

V

Input Logic 0 Voltage

0.8

V

Input Logic 1 Current

10

nA

Input Logic 0 Current

20

nA

Input Capacitance

2

pF

SDIO, SDO (OUTPUTS)

Output Logic 1 Voltage

2.7

V

Output Logic 0 Voltage

0.4

V

TIMING

Clock Rate (SCLK, 1/tSCLK)

25

MHz

Pulse Width High, tHIGH

16

ns

Pulse Width Low, tLOW

16

ns

SDIO to SCLK Setup, tDS

2

ns

SCLK to SDIO Hold, tDH

1.1

ns

SCLK to Valid SDIO and SDO, tDV

8

ns

CS to SCLK Setup and Hold, tS, tH

2

ns

CS Minimum Pulse Width High, tPWH

3

ns

相关PDF资料 |

PDF描述 |

|---|---|

| AD9518-0ABCPZ | IC CLOCK GEN 6CH 2.8GHZ 48LFCSP |

| AD9518-1ABCPZ | IC CLOCK GEN 6CH 2GHZ 48LFCSP |

| AD9518-2ABCPZ-RL7 | IC CLOCK GEN 6CH 2.2GHZ 48LFCSP |

| AD9518-3ABCPZ | IC CLOCK GEN 6CH 2GHZ 48LFCSP |

| AD9518-4ABCPZ-RL7 | IC CLOCK GEN 6CH 1.8GHZ 48LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9517-4APCBZ | 制造商:AD 制造商全称:Analog Devices 功能描述:12-Output Clock Generator with Integrated 1.6 GHz VCO |

| AD9517-4BCPZ | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述:IC CLOCK GENERATOR 1.8GHZ LFCSP-48 制造商:Analog Devices 功能描述:IC, CLOCK GENERATOR, 1.8GHZ, LFCSP-48, Clock IC Type:Clock Generator, Frequency: |

| AD9517-4BCPZ-REEL7 | 制造商:Analog Devices 功能描述: |

| AD9518-0 | 制造商:AD 制造商全称:Analog Devices 功能描述:6-Output Clock Generator |

| AD9518-0/PCBZ | 制造商:Analog Devices 功能描述:Evaluation Kit For 6-Output Clock Generator With Integrated 2.8 GHZ VCO |

发布紧急采购,3分钟左右您将得到回复。