- 您现在的位置:买卖IC网 > PDF目录9093 > AD9572ACPZPEC-RL (Analog Devices Inc)IC PLL CLOCK GEN 25MHZ 40LFCSP PDF资料下载

参数资料

| 型号: | AD9572ACPZPEC-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 2/20页 |

| 文件大小: | 0K |

| 描述: | IC PLL CLOCK GEN 25MHZ 40LFCSP |

| 标准包装: | 2,500 |

| 类型: | 时钟发生器,扇出配送,多路复用器 |

| PLL: | 是 |

| 输入: | 晶体 |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:7 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 156.25MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 2.97 V ~ 3.63 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-WFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP-WQ(6x6) |

| 包装: | 带卷 (TR) |

AD9572

Rev. B | Page 10 of 20

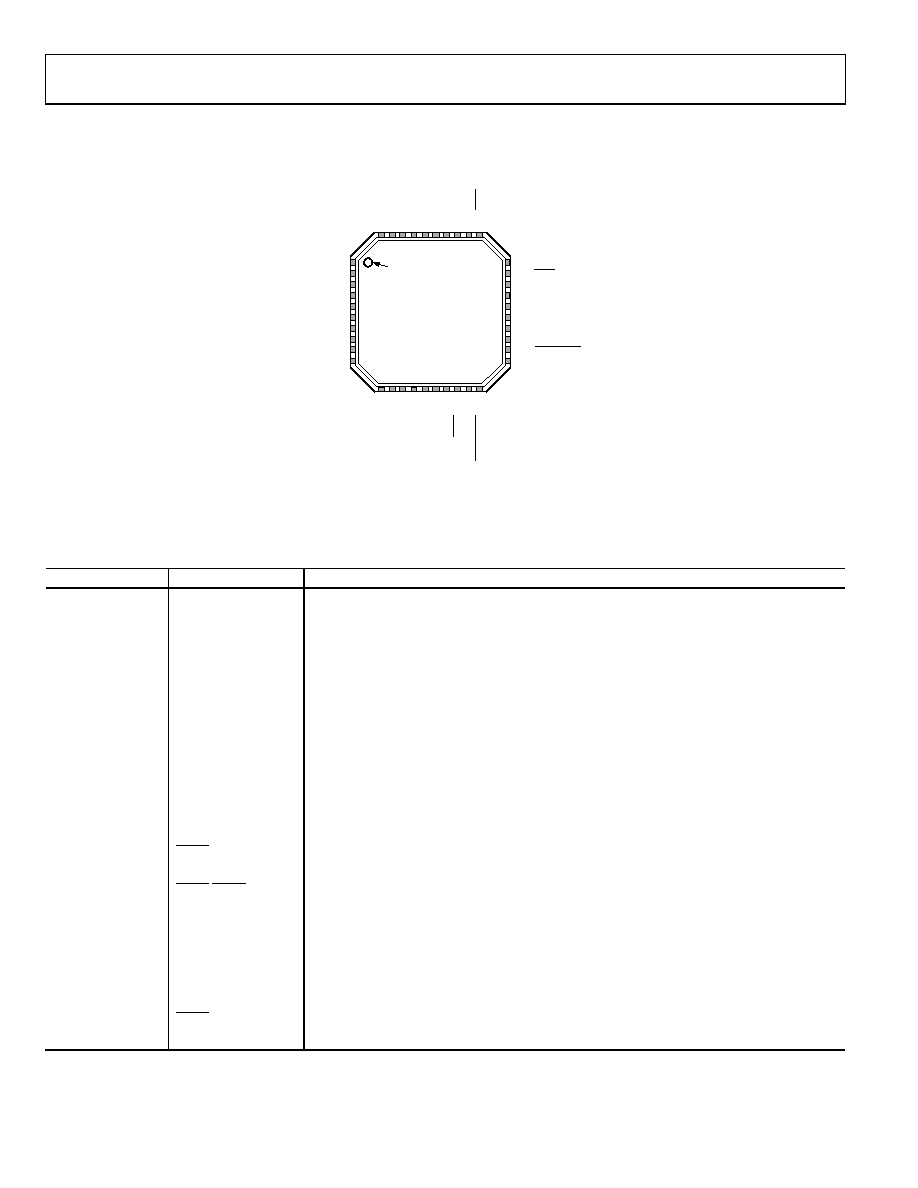

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

NOTES

1. * = SHORT TO PIN 36.

2. ** = SHORT TO PIN 14.

3. NC = NO CONNECT.

4. NOTE THAT THE EXPOSED PADDLE ON THIS PACKAGE IS AN ELECTRICAL

CONNECTION AS WELL AS A THERMAL ENHANCEMENT. FOR THE DEVICE TO

FUNCTION PROPERLY, THE PADDLE MUST BE ATTACHED TO GROUND (GND).

PIN 1

INDICATOR

1

GND

2

VS

3

NC

4

25M

5

VS

6

XO

7

XO

8

REFCLK

9

REFSEL

10

GND

23 33M

24 VS

25 VS

26 VS

27 FREQSEL

28 VS

29 106M

30 106M

22 100M/125M

21 100M/125M

11

V

S

12

**

13

**

15

V

S

17

15

6M

16

V

S

18

15

6M

19

10

0M

/1

25

M

20

10

0M

/1

25

M

14

B

Y

P

A

S

2

33

V

S

34

G

N

D

35

V

S

36

B

Y

P

A

S

1

37

F

O

R

C

E

_L

O

W

38

*

39

V

S

40

V

S

32

10

6M

31

10

6M

TOP VIEW

(Not to Scale)

AD9572

0

749

8-

0

07

Figure 6. Pin Configuration

Pin No.

Mnemonic

Description

1, 10, 34

GND

Ground. Includes external paddle (EPAD).

2

VS

Power Supply Connection for the 25M CMOS Buffer.

3

NC

No Connect. This pin should be left floating.

4

25M

CMOS 25 MHz Output.

5

VS

Power Supply Connection for the Crystal Oscillator.

6, 7

XO

External 25 MHz Crystal.

8

REFCLK

25 MHz Reference Clock Input. Tie low when not in use.

9

REFSEL

Logic Input. Used to select the reference source.

11

VS

Power Supply Connection for the GbE PLL.

12, 13

N/A

Short to Pin 14.

14, 36

BYPASS2, BYPASS1

These pins are for bypassing each LDO to ground with a 220 nF capacitor.

15

VS

Power Supply Connection for the GbE VCO.

16

VS

Power Supply Connection for the 156M LVDS Output Buffer and Output Dividers.

17

156M

LVPECL/LVDS Output at 156.25 MHz.

18

156M

Complementary LVPECL/LVDS Output at 156.25 MHz.

19, 21

100M/125M

LVPECL/LVDS Output at 100 MHz or 125 MHz. Selected by FREQSEL pin strapping.

20, 22

100M/125M

Complementary LVPECL/LVDS Output at 100 MHz or 125 MHz.

23

33M

CMOS 33.33 MHz Output.

24

VS

Power Supply Connection for the 33M CMOS Output Buffer and Output Dividers.

25

VS

Power Supply Connection for the 100M/125M LVDS Output Buffer and Output Dividers.

26

VS

Power Supply Connection for the GbE PLL Feedback Divider.

27

FREQSEL

Logic Input. Used to configure output drivers.

28

VS

Power Supply Connection for the FC PLL Feedback Divider.

29, 31

106M

LVPECL/LVDS Output at 106.25 MHz.

30, 32

106M

Complementary LVPECL/LVDS Output at 106.25 MHz.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-BTN-MV-S | CONVERTER MOD DC/DC 18.5V 150W |

| X9410WP24I-2.7 | IC XDCP DUAL 64-TAP 10K 24-DIP |

| X9410WP24I | IC XDCP DUAL 64-TAP 10K 24-DIP |

| D38999/20JD15JD | CONN RCPT 15POS WALL MNT W/SCKT |

| AD9571ACPZPEC-RL | IC PLL CLOCK GEN 25MHZ 40LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9572-EVALZ-LVD | 制造商:AD 制造商全称:Analog Devices 功能描述:Fiber Channel/Ethernet Clock Generator IC, PLL Core, Dividers, 7 Clock Outputs |

| AD9572-EVALZ-PEC | 制造商:AD 制造商全称:Analog Devices 功能描述:Fiber Channel/Ethernet Clock Generator IC, PLL Core, Dividers, 7 Clock Outputs |

| AD9572XCPZLVD | 制造商:Analog Devices 功能描述: |

| AD9572XCPZPEC | 制造商:Analog Devices 功能描述: |

| AD9573 | 制造商:AD 制造商全称:Analog Devices 功能描述:PCI-Express Clock Generator IC, PLL Core, Dividers, Two Outputs |

发布紧急采购,3分钟左右您将得到回复。