参数资料

| 型号: | AD9734BBCZRL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 56/72页 |

| 文件大小: | 0K |

| 描述: | IC DAC 10BIT 1.2GSPS 160-CSPBGA |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 标准包装: | 1,500 |

| 位数: | 10 |

| 数据接口: | 并联 |

| 转换器数目: | 1 |

| 电压电源: | 模拟和数字 |

| 功率耗散(最大): | 550mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 160-LFBGA,CSPBGA |

| 供应商设备封装: | 160-CSPBGA(12x12) |

| 包装: | 带卷 (TR) |

| 输出数目和类型: | 2 电流,单极 |

| 采样率(每秒): | 1.2G |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页当前第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

AD9734/AD9735/AD9736

Rev. A | Page 6 of 72

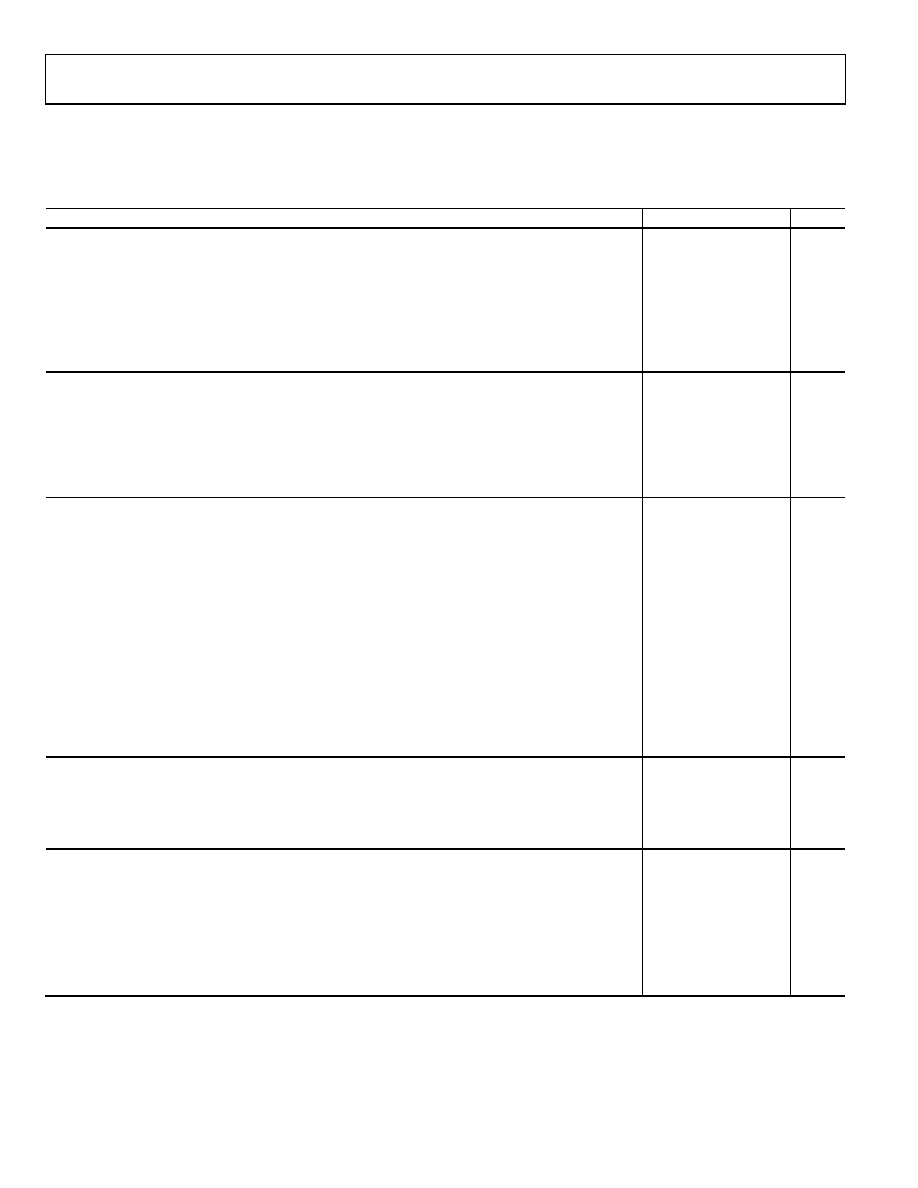

DIGITAL SPECIFICATIONS

AVDD33 = DVDD33 = 3.3 V, CVDD18 = DVDD18 = 1.8 V, maximum sample rate, IFS = 20 mA, 1× mode, 25 Ω, 1% balanced load,

unless otherwise noted. LVDS drivers and receivers are compliant to the IEEE-1596 reduced range link, unless otherwise noted.

Table 2.

Parameter

Min

Typ

Max

Unit

LVDS DATA INPUT

(DB[13:0]+, DB[13:0]) DB+ = VIA, DB = VIB

Input Voltage Range, VIA or VIB

825

1575

mV

Input Differential Threshold, VIDTH

100

+100

mV

Input Differential Hysteresis, VIDTHH VIDTHL

20

mV

Receiver Differential Input Impedance, RIN

80

120

Ω

LVDS Input Rate

1200

MSPS

LVDS Minimum Data Valid Period (tMDE)

344

ps

LVDS CLOCK INPUT

(DATACLK_IN+, DATACLK_IN) DATACLK_IN+ = VIA, DATACLK_IN = VIB

Input Voltage Range, VIA or VIB

825

1575

mV

Input Differential Threshold,1 VIDTH

100

+100

mV

Input Differential Hysteresis, VIDTHH VIDTHL

20

mV

Receiver Differential Input Impedance, RIN

80

120

Ω

Maximum Clock Rate

600

MHz

LVDS CLOCK OUTPUT

(DATACLK_OUT+, DATACLK_ OUT) DATACLK_OUT+ = Voa, DATACLK_OUT = Vob 100 Ω Termination

Output Voltage High, VOA or VOB

1375

mV

Output Voltage Low, VOA or VOB

1025

mV

Output Differential Voltage, |VOD|

150

200

250

mV

Output Offset Voltage, VOS

1150

1250

mV

Output Impedance, Single-Ended, RO

80

100

120

Ω

RO Mismatch Between A and B,

ΔRO

10

%

Change in |VOD| Between 0 and 1, |

ΔVOD|

25

mV

Change in VOS Between 0 and 1,

ΔVOS

25

mV

Output Current—Driver Shorted to Ground, ISA, ISB

20

mA

Output Current—Drivers Shorted Together, ISAB

4

mA

Power-Off Output Leakage, |IXA|, |IXB|

10

mA

Maximum Clock Rate

600

MHz

DAC CLOCK INPUT (CLK+, CLK)

Input Voltage Range, CLK or CLK+

0

800

Differential Peak-to-Peak Voltage

400

800

1600

mV

Common-Mode Voltage

300

400

500

mV

Maximum Clock Rate

1200

MHz

SERIAL PERIPHERAL INTERFACE

Maximum Clock Rate (fSCLK, 1/tSCLK)

20

MHz

Minimum Pulse Width High, tPWH

20

ns

Minimum Pulse Width Low, tPWL

20

ns

Minimum SDIO and CSB to SCLK Setup, tDS

10

ns

Minimum SCLK to SDIO Hold, tDH

5

ns

Maximum SCLK to Valid SDIO and SDO, tDV

20

ns

Minimum SCLK to Invalid SDIO and SDO, tDNV

5

ns

相关PDF资料 |

PDF描述 |

|---|---|

| VI-B3P-MY-B1 | CONVERTER MOD DC/DC 13.8V 50W |

| VI-230-MW-B1 | CONVERTER MOD DC/DC 5V 100W |

| VI-B3N-MY-B1 | CONVERTER MOD DC/DC 18.5V 50W |

| LTC1599BCG#TRPBF | IC D/A CONV 16BIT MLTPLYNG24SSOP |

| VI-B3M-MY-B1 | CONVERTER MOD DC/DC 10V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9734BBCZRL1 | 制造商:AD 制造商全称:Analog Devices 功能描述:10-/12-/14-Bit, 1200 MSPS DACS |

| AD9734-DPG2-EBZ | 功能描述:BOARD EVAL FOR AD9734 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| AD9734-EB | 制造商:Analog Devices 功能描述:EVAL BD FOR AD9735 DAC, 10-/12-/14BIT, 1200 MSPS DACS - Trays |

| AD9734-EBZ | 制造商:Analog Devices 功能描述:EVAL BD FOR AD9735 DAC, 10-/12-/14BIT, 1200 MSPS DACS - Bulk |

| AD9735 | 制造商:AD 制造商全称:Analog Devices 功能描述:14/12/10-Bit, 1200 MSPS D/A Converters |

发布紧急采购,3分钟左右您将得到回复。