参数资料

| 型号: | AD9760ARU50 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 5/23页 |

| 文件大小: | 0K |

| 描述: | IC DAC 10BIT 50MSPS 28-TSSOP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 标准包装: | 50 |

| 系列: | TxDAC® |

| 设置时间: | 35ns |

| 位数: | 10 |

| 转换器数目: | 1 |

| 电压电源: | 模拟和数字 |

| 功率耗散(最大): | 175mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 28-TSSOP |

| 包装: | 管件 |

| 输出数目和类型: | 2 电流,单极;2 电流,双极 |

| 采样率(每秒): | 60M |

| 配用: | AD9760-EBZ-ND - BOARD EVAL FOR AD9760 |

AD9760

–13–

REV. B

The optimum distortion performance for any reconstructed

waveform is obtained with a 0.1

F external capacitor installed.

Thus, if IREF is fixed for an application, a 0.1

F ceramic chip

capacitor is recommended. Also, since the control amplifier is

optimized for low power operation, multiplying applications

requiring large signal swings should consider using an external

control amplifier to enhance the application’s overall large signal

multiplying bandwidth and/or distortion performance.

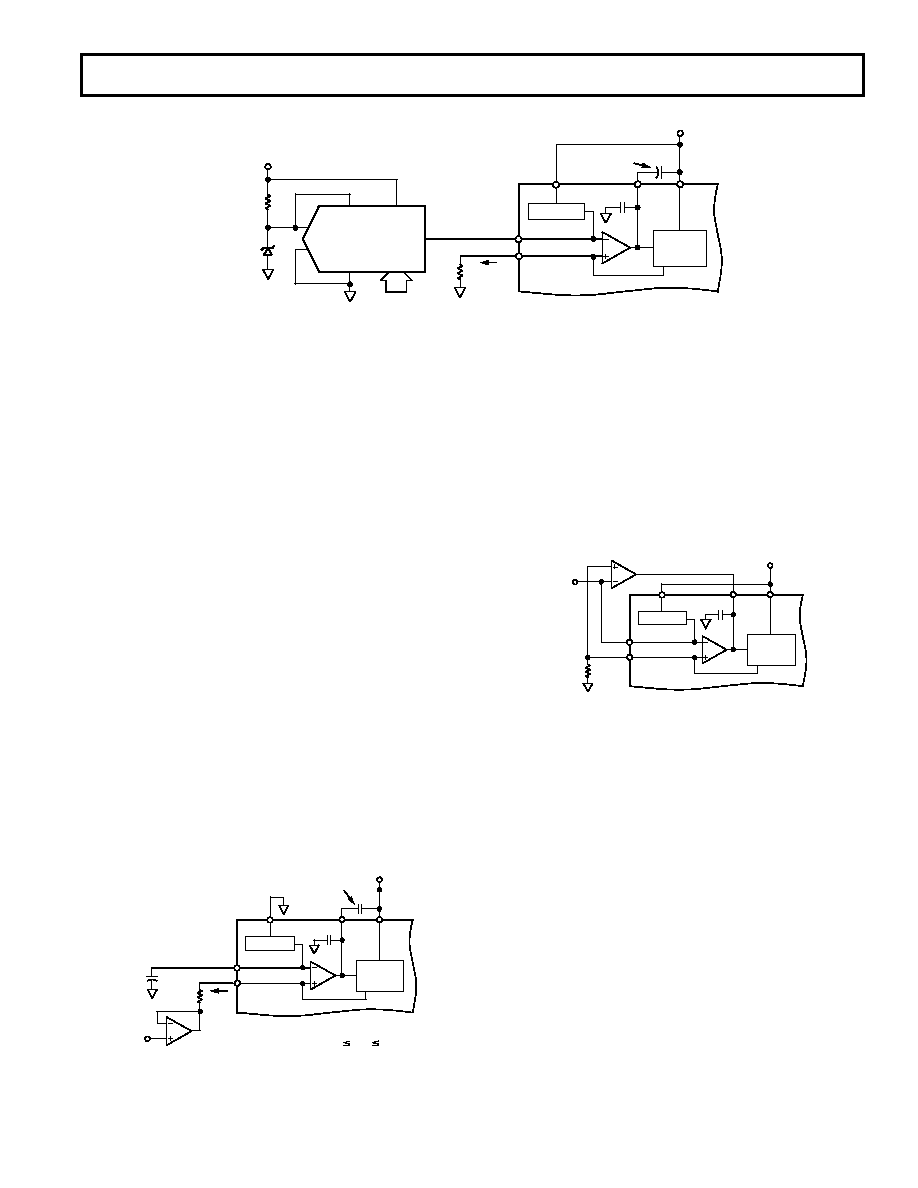

There are two methods in which IREF can be varied for a fixed

RSET. The first method is suitable for a single-supply system in

which the internal reference is disabled, and the common-mode

voltage of REFIO is varied over its compliance range of 1.25 V

to 0.10 V. REFIO can be driven by a single-supply amplifier or

DAC, allowing IREF to be varied for a fixed RSET. Since the

input impedance of REFIO is approximately 1 M

, a simple,

low cost R-2R ladder DAC configured in the voltage mode

topology may be used to control the gain. This circuit is shown

in Figure 43 using the AD7524 and an external 1.2 V reference,

the AD1580.

The second method may be used in a dual-supply system in

which the common-mode voltage of REFIO is fixed and IREF is

varied by an external voltage, VGC, applied to RSET via an ampli-

fier. An example of this method is shown in Figure 44 where

the internal reference is used to set the common-mode voltage

of the control amplifier to 1.20 V. The external voltage, VGC, is

referenced to ACOM and should not exceed 1.2 V. The value

of RSET is such that IREFMAX and IREFMIN do not exceed 62.5

A

and 625

A, respectively. The associated equations in Figure 44

can be used to determine the value of RSET.

50pF

COMP1

+1.2V REF

AVDD

REFLO

CURRENT

SOURCE

ARRAY

AVDD

REFIO

FS ADJ

RSET

AD9760

IREF

OPTIONAL

BANDLIMITING

CAPACITOR

VGC

1 F

IREF = (1.2 – VGC)/RSET

WITH VGC < VREFIO AND 62.5 A

IREF

625A

Figure 44. Dual-Supply Gain Control Circuit

In some applications, the user may elect to use an external con-

trol amplifier to enhance the multiplying bandwidth, distortion

performance and/or settling time. External amplifiers capable of

driving a 50 pF load such as the AD817 are suitable for this

purpose. It is configured in such a way that it is in parallel with

the weaker internal reference amplifier as shown in Figure 45.

In this case, the external amplifier simply overdrives the weaker

reference control amplifier. Also, since the internal control

amplifier has a limited current output, it will sustain no damage

if overdriven.

50pF COMP1

+1.2V REF

AVDD

REFLO

CURRENT

SOURCE

ARRAY

AVDD

REFIO

FS ADJ

RSET

AD9760

VREF

INPUT

EXTERNAL

CONTROL AMPLIFIER

Figure 45. Configuring an External Reference Control

Amplifier

ANALOG OUTPUTS

The AD9760 produces two complementary current outputs,

IOUTA and IOUTB, which may be configured for single-ended or

differential operation. IOUTA and IOUTB can be converted into

complementary single-ended voltage outputs, VOUTA and VOUTB,

via a load resistor, RLOAD, as described in the DAC Transfer

Function section by Equations 5 through 8. The differential

voltage, VDIFF, existing between VOUTA and VOUTB can also be

converted to a single-ended voltage via a transformer or differ-

ential amplifier configuration. The ac performance of the AD9760

is optimum and specified using a differential transformer

coupled output in which the voltage swing at IOUTA and IOUTB is

limited to

±0.5 V. If a single-ended unipolar output is desirable,

IOUTA should be selected.

The distortion and noise performance of the AD9760 can be

enhanced when the AD9760 is configured for differential opera-

tion. The common-mode error sources of both IOUTA and IOUTB

can be significantly reduced by the common-mode rejection of a

transformer or differential amplifier. These common-mode

error sources include even-order distortion products and noise.

1.2V

50pF

COMP1

+1.2V REF

AVDD

REFLO

CURRENT

SOURCE

ARRAY

AVDD

REFIO

FS ADJ

RSET

AD9760

IREF =

VREF/RSET

AVDD

OPTIONAL

BANDLIMITING

CAPACITOR

VREF

VDD

RFB

OUT1

OUT2

AGND

DB7–DB0

AD7524

AD1580

0.1V TO 1.2V

Figure 43. Single-Supply Gain Control Circuit

相关PDF资料 |

PDF描述 |

|---|---|

| AD7533JP | IC DAC 10BIT MULTIPLYING 20-PLCC |

| V300A48H400BF2 | CONVERTER MOD DC/DC 48V 400W |

| LTC2753IUK-12#PBF | IC DAC 12BIT DUAL 48-QFN |

| V300A3V3H264BL | CONVERTER MOD DC/DC 3.3V 264W |

| AD421BRZRL | IC DAC 16BIT LOOP 4-20MA 16SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9760ARU50RL | 功能描述:INTEGRATED CIRCUIT 制造商:analog devices inc. 系列:* 包装:带卷(TR) 零件状态:最後搶購 封装/外壳:28-TSSOP(0.173",4.40mm 宽) 供应商器件封装:28-TSSOP 标准包装:1 |

| AD9760ARU50RL7 | 功能描述:IC DAC 10BIT 50MSPS 28-TSSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:TxDAC® 标准包装:47 系列:- 设置时间:2µs 位数:14 数据接口:并联 转换器数目:1 电压电源:单电源 功率耗散(最大):55µW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:管件 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):* |

| AD9760ARURL | 功能描述:INTEGRATED CIRCUIT 制造商:analog devices inc. 系列:* 包装:带卷(TR) 零件状态:最後搶購 封装/外壳:28-TSSOP(0.173",4.40mm 宽) 供应商器件封装:28-TSSOP 标准包装:1 |

| AD9760ARURL7 | 制造商:Analog Devices 功能描述:DAC 1-CH 10-bit 28-Pin TSSOP T/R 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD9760ARUZ | 功能描述:IC DAC 10BIT 125MSPS 28-TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:TxDAC® 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:50 系列:- 设置时间:4µs 位数:12 数据接口:串行 转换器数目:2 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-TSSOP,8-MSOP(0.118",3.00mm 宽) 供应商设备封装:8-uMAX 包装:管件 输出数目和类型:2 电压,单极 采样率(每秒):* 产品目录页面:1398 (CN2011-ZH PDF) |

发布紧急采购,3分钟左右您将得到回复。