- 您现在的位置:买卖IC网 > PDF目录4594 > ADATE302-02BSVZ (Analog Devices Inc)IC DCL ATE 500MHZ DUAL 100TQFP PDF资料下载

参数资料

| 型号: | ADATE302-02BSVZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 40/58页 |

| 文件大小: | 0K |

| 描述: | IC DCL ATE 500MHZ DUAL 100TQFP |

| 标准包装: | 1 |

| 类型: | DCL |

| 应用: | 自动测试设备 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-TQFP 裸露焊盘 |

| 供应商设备封装: | 100-TQFP-EP(14x14) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页当前第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

ADATE302-02

Rev. A | Page 45 of 58

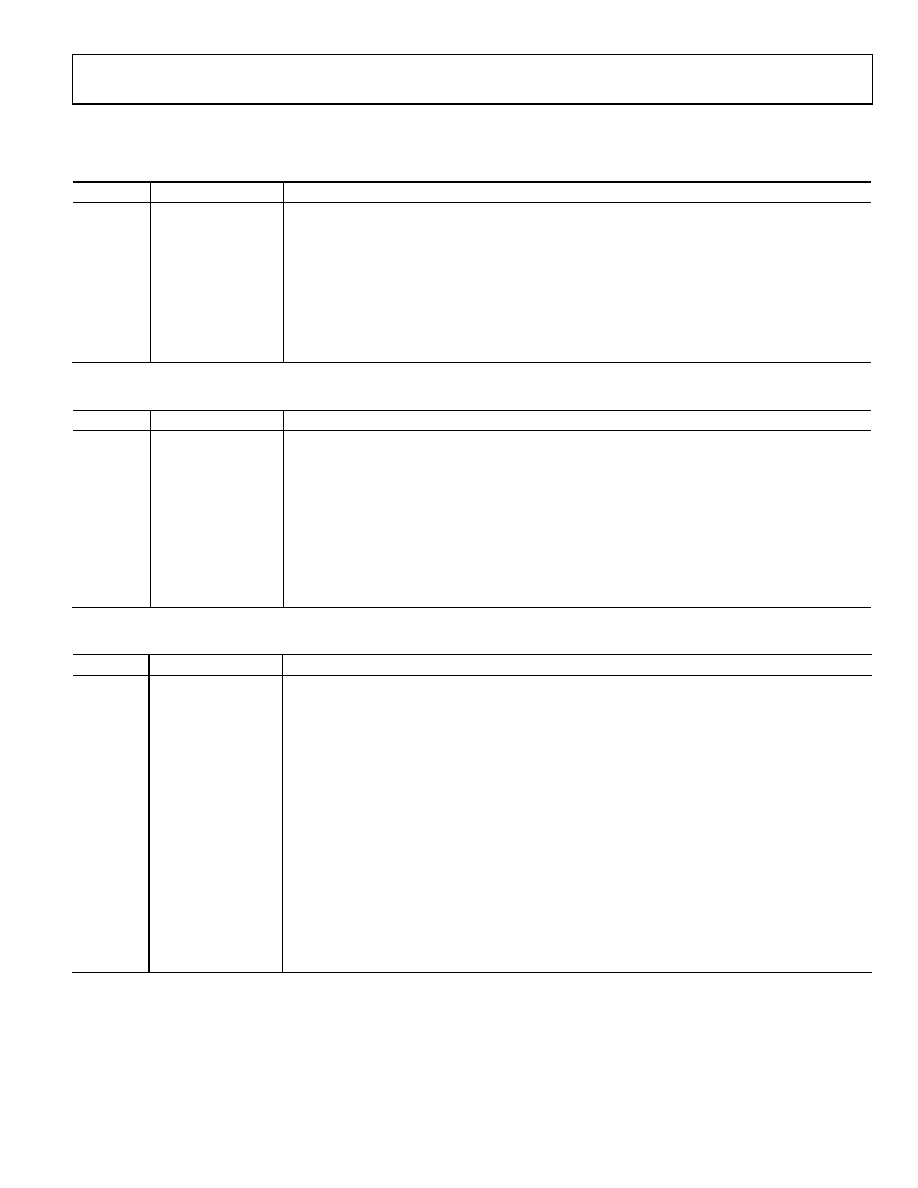

DETAILS OF REGISTERS

Table 22. PE/PMU Enable (ADDR[4:0] = 0x0C)

Bit

Name

Description

Data[2]

PMU enable

0 = disable PMU force output and clamps, place PMU in MV mode

1 = enable PMU force output

When set to 0, the PMU State bits are ignored, except for PMU Sense Path (Data[7]).

Data[1]

Force VT

0 = normal driver operation

1 = force driver to VT

See Table 30 for complete functionality of this bit.

Data[0]

PE disable

0 = enable driver functions

1 = disable driver (low leakage)

See Table 30 for complete functionality of this bit.

Table 23. Channel State (ADDR[4:0] = 0x0D)

Bit

Name

Description

Data[2]

HVOUT mode select

0 = HVOUT driver in low impedance

1 = enable HVOUT driver

This bit affects Channel 0 only. Ensure that Channel 0 bit in SPI write is active.

Channel 1 bit in SPI write is don’t care.

Data[1]

Load enable

0 = disable load

1 = enable load

See Table 30 for complete functionality of this bit.

Data[0]

Driver high-Z/VT

0 = enable driver high-Z function

1 = enable driver VTERM function

See Table 30 for complete functionality of this bit.

Table 24. PMU State (ADDR[4:0] = 0x0E)1, 2

Bit

Name

Description

Data[9:8]

PMU input selection

00 = VDUTGND (calibrated for 0.0 V voltage reference)

01 = 2.5 V + VDUTGND (calibrated for 0.0 A current reference)

1X = PMUDAC

Data[7]

PMU sense path

0 = internal sense

1 = external sense

Data[6]

Reserved

Data[5]

PMU clamp enable

0 = disable clamps

1 = enable clamps

Data[4]

PMU measure V/I

0 = measure voltage mode

1 = measure current mode

Data[3]

PMU force V/I

0 = force voltage mode

1 = force current mode

Data[2:0]

PMU range

0XX = Range E (2 μA)

100 = Range D (20 μA)

101 = Range C (200 μA)

110 = Range B (2 mA)

111 = Range A (25 mA)

1 Note that when the ADDR[4:0] = 0x0C PMU enable bit (Data[2]) = 0, the PMU force outputs and clamps are disabled, and the PMU is placed into measure voltage

mode. Data[9:8] and Data[6:0] of the PMU state register are ignored, and only Data[7], the PMU sense path bit, is valid.

2 X = don’t care.

相关PDF资料 |

PDF描述 |

|---|---|

| RMM43DSEF | CONN EDGECARD 86POS .156 EYELET |

| RSM43DRTF | CONN EDGECARD 86POS DIP .156 SLD |

| RMM43DRTF | CONN EDGECARD 86POS DIP .156 SLD |

| RSM44DRKN | CONN EDGECARD 88POS DIP .156 SLD |

| RSM44DRKH | CONN EDGECARD 88POS DIP .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADATE302BBCZ-02 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| ADATE302BSVZ | 制造商:Analog Devices 功能描述: |

| ADATE303BBCZ | 制造商:Analog Devices 功能描述: |

| ADATE304 | 制造商:AD 制造商全称:Analog Devices 功能描述:200 MHz Dual Integrated DCL with Level Setting DACs, Per Pin PMU, and Per Chip VHH |

| ADATE304BBCZ | 功能描述:IC DCL ATE 200MHZ DUAL 84CSPBGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

发布紧急采购,3分钟左右您将得到回复。