- 您现在的位置:买卖IC网 > PDF目录2064 > ADAV4622BSTZ (Analog Devices Inc)IC AUD PRO ATV/SIF DECODE 80LQFP PDF资料下载

参数资料

| 型号: | ADAV4622BSTZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 18/28页 |

| 文件大小: | 0K |

| 描述: | IC AUD PRO ATV/SIF DECODE 80LQFP |

| 标准包装: | 1 |

| 系列: | SigmaDSP® |

| 类型: | 解调器 |

| 应用: | 家用音频 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 80-LQFP |

| 供应商设备封装: | 80-LQFP(14x14) |

| 包装: | 托盘 |

| 配用: | EVAL-ADAV4622EBZ-ND - BOARD EVAL ADAV4622 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

ADAV4622

Rev. B | Page 25 of 2

8

S/PDIF INPUT/OUTPUT

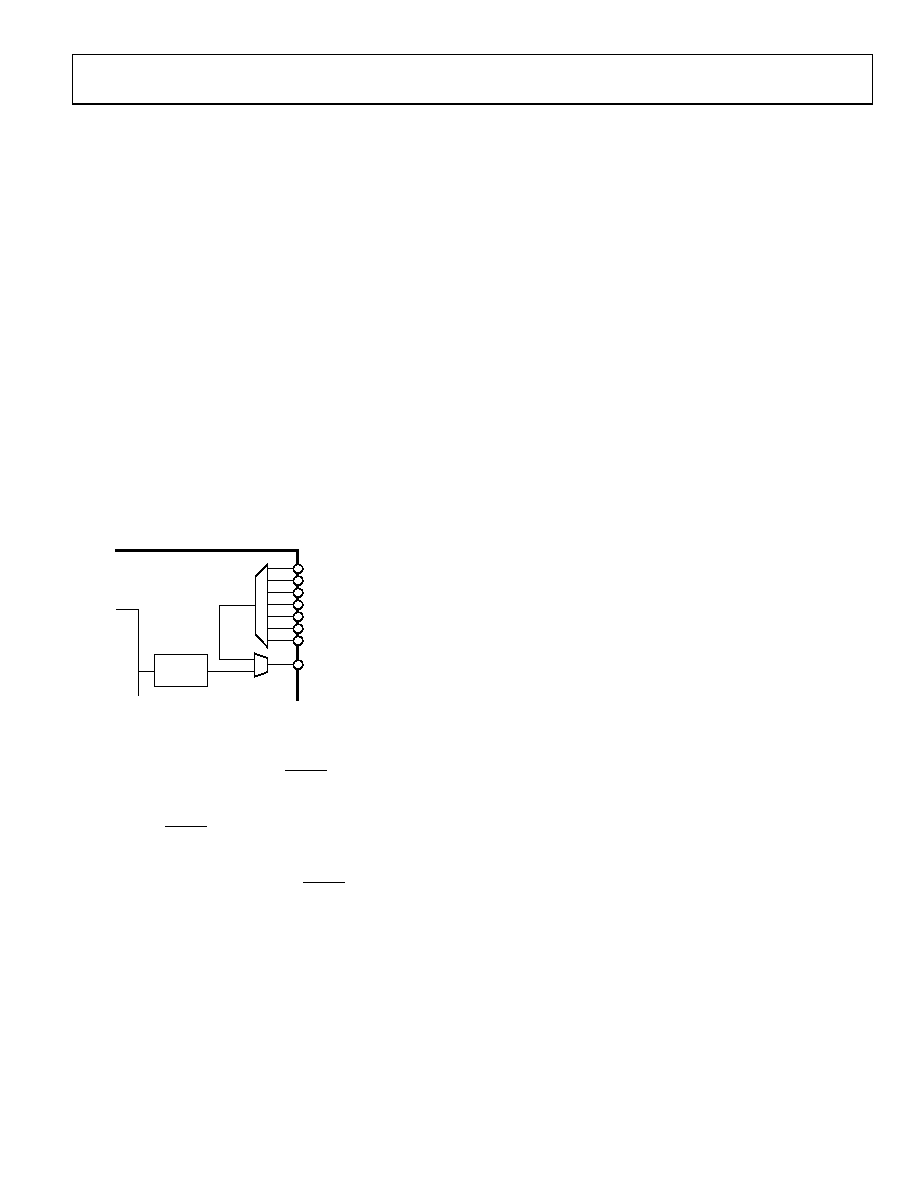

The S/PDIF output (SPDIF_OUT/SDO1) uses a multiplexer to

select an output from the audio processor or to pass through the

unprocessed SPDIF_IN signals, as shown in Figure 32. On the

ADAV4622, the S/PDIF inputs, SPDIF_IN0/SPDIF_IN1/

SPDIF_IN2/SPDIF_IN3/SPDIF_IN4/SPDIF_IN5/SPDIF_IN6,

are available on the SDIN3, LRCLK0, BCLK0, LRCLK1,

BCLK1, LRCLK2, and BCLK2 pins, respectively. It is possible to

have all seven S/PDIF inputs connected to different S/PDIF

signals at one time. A consequence of this setup is that none of

the LRCLKs and BCLKs are available for use with the digital

inputs SDIN0, SDIN1, SDIN2, and SDIN3. If there is only one

S/PDIF input in use, using the SDIN3 pin as the dedicated

S/PDIF input is recommended; this enables BCLK0/LRCLK0,

BCLK1/LRCLK1, and BCLK2/LRCLK2 to be used as the clock

and framing signal for the synchronous and asynchronous port.

If SDIN3 is used as an S/PDIF input, it should not be used

internally as an input to the audio processor because it contains

invalid data. Similarly, if BCLK or LRCLK are used as S/PDIF

inputs, they can no longer be used as the clock and framing

signals for SDIN0, SDIN1, SDIN2, and SDIN3. The S/PDIF

encoder supports only consumer formats that conform to

IEC-600958.

SDIN3 (SPDIF_IN0)

LRCLK0 (SPDIF_IN1)

BCLK0 (SPDIF_IN2)

LRCLK1 (SPDIF_IN3)

BCLK1 (SPDIF_IN4)

LRCLK2 (SPDIF_IN5)

BCLK2 (SPDIF_IN6)

SDO1 (SPDIF_OUT)

S/PDIF

ENCODER

0

706

8-

0

29

Figure 32. S/PDIF Output

HARDWARE MUTE CONTROL

The ADAV4622 mute input can be used to mute any of the

analog or digital outputs. When the MUTE pin goes low, the

selected outputs ramp to a muted condition. Unmuting is

handled in one of two ways and depends on the register setting.

By default, the MUTE pin going high causes the outputs to

immediately ramp to an unmuted state. However, it is also

possible to have the unmute operation controlled by a control

register bit. In this scenario, even if the MUTE pin goes high,

the device does not unmute until a bit in the control register is

set. This can be used when the user wants to keep the outputs

muted, even after the pin has gone high again, for example, in

the case of a fault condition. This allows the system controller

total control over the unmute operation.

Full details on register settings and operation of the mute function

are available upon request. Contact a local Analog Devices sales

representative for more details.

AUDIO PROCESSOR

The internal audio processor runs at 2560 × fS; at 48 kHz, this

is 122.88 MHz. Internally, the word size is 28 bits, which allows

24 dB of headroom for internal processing. Designed specific-

ally with audio processing in mind, it can implement complex

audio algorithms efficiently.

By default, the ADAV4622 loads a default audio flow, as shown

in Figure 34. However, because the audio processor is fully

programmable, a custom audio flow can be quickly developed

and loaded to the audio processor.

The audio flow is contained in program RAM and parameter

RAM. Program RAM contains the instructions to be processed

by the audio processor, and parameter RAM contains the

coefficients that control the flow, such as volume control, filter

coefficients, and enable bits.

GRAPHICAL PROGRAMMING ENVIRONMENT

Custom flows for the ADAV4622 are created in a powerful

drag-and-drop graphical programming application. No knowl-

edge of assembly code is required to program the ADAV4622.

Featuring a comprehensive library of audio processing blocks

(such as filters, delays, dynamics processors, and third-party

algorithms), it allows the quick and simple creation of custom

flows. For debugging purposes, run-time control of the audio

flow allows the user to fully configure and test the created flow.

Training materials and support are available upon request.

Contact a local Analog Devices sales representative for more

details.

APPLICATION LAYER

Unique to this family is the embedded application layer, which

allows the user to define a custom set of registers to control the

audio flow, greatly simplifying the interface between the audio

processor and the system controller.

Once a custom flow is created, a user-customized register map

can be defined for controlling the flow. Each register is 16 bits,

but controls can use only one bit or all 16 bits. Users have full

control over which parameters they control and the degree of

control they have over those parameters during run time. The

combination of the graphical programming environment and

the powerful application layer allows the user to quickly develop

a custom audio flow and still maintain the usability of a simple

register-based device.

Comprehensive documentation on developing a custom audio

flow and the definition and creation of the custom application

layer for the ADAV4622 is available upon request. Contact a

local Analog Devices sales representative for more details.

相关PDF资料 |

PDF描述 |

|---|---|

| ADCLK846BCPZ-REEL7 | IC CLK BUFFER 1:6 1.2GHZ 24LFCSP |

| ADCLK854BCPZ | IC CLOCK BUFFER MUX 2:12 48LFCSP |

| ADCLK907BCPZ-WP | IC CLK/DATA BUFF DVR 1:1 16LFCSP |

| ADCLK914BCPZ-WP | IC CLK/DATA BUFF DVR 1:1 16LFCSP |

| ADCLK944BCPZ-R7 | IC CLOCK BUFFER 1:4 7GHZ 16LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADAV4-KIT-1 | 制造商:Wiebetech 功能描述:Combo Dock Kit #1 for Weibetech Ultradock Series |

| ADAV801 | 制造商:AD 制造商全称:Analog Devices 功能描述:Audio Codec for Recordable DVD |

| ADAV801AST | 制造商:Analog Devices 功能描述:AUDIO CODEC FOR RECORDABLE DVD - Bulk |

| ADAV801ASTZ | 功能描述:IC CODEC AUDIO R-DVD 3.3V 64LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

| ADAV801ASTZ-REEL | 功能描述:IC CODEC AUDIO R-DVD 3.3V 64LQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。