- 您现在的位置:买卖IC网 > PDF目录378277 > ADC0811BCN (NATIONAL SEMICONDUCTOR CORP) 8-Bit Serial I/O A/D Converter With 11-Channel Multiplexer PDF资料下载

参数资料

| 型号: | ADC0811BCN |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | ADC |

| 英文描述: | 8-Bit Serial I/O A/D Converter With 11-Channel Multiplexer |

| 中文描述: | 11-CH 8-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDIP20 |

| 封装: | 0.300 INCH, PLASTIC, DIP-20 |

| 文件页数: | 10/14页 |

| 文件大小: | 323K |

| 代理商: | ADC0811BCN |

Functional Description

(Continued)

at least 64

w

2

clocks to insure that the A/D has completed

its conversion. If S

CLK

is enabled sooner, synchronizing to

the data output on DO is not possible since an end of con-

version signal from the A/D is not available and the actual

conversion time is not known. With CS low during the con-

version time (64

w

2

max) DO will go low after the eighth

falling edge of S

CLK

and remain low until the conversion is

completed. Once the conversion is through DO will transmit

the MSB. The rest of the data will be shifted out once S

CLK

is enabled as discussed previously.

If CS goes high during the conversion sequence DO is tri-

stated, and the result is not affected so long as CS remains

high until the end of the conversion.

1.2 MULTIPLEXER ADDRESSING

The four bit mux address is shifted, MSB first, into DI. Input

data corresponds to the channel selected as shown in table

1. Care should be taken not to send an address greater than

or equal to twelve (11XX) as this puts the A/D in a digital

testing mode. In this mode the analog inputs CH0 thru CH3

become digital outputs, for our use in production testing.

2.0 ANALOG INPUT

2.1 THE INPUT SAMPLE AND HOLD

The ADC0811’s sample/hold capacitor is implemented in its

capacitive ladder structure. After the channel address is re-

ceived, the ladder is switched to sample the proper analog

input. This sampling mode is maintained for 1

m

sec after the

eighth S

CLK

falling edge. The hold mode is initiated with the

start of the conversion process. An acquisition window of

4t

SCLK

a

1

m

sec is therefore available to allow the ladder

capacitance to settle to the analog input voltage. Any

change in the analog voltage before or after the acquisition

window will not effect the A/D conversion result.

In the most simple case, the ladder’s acquisition time is de-

termined by the R

on

(3K) of the multiplexer switches and the

total ladder capacitance (90pf). These values yield an acqui-

sition time of about 2

m

sec for a full scale reading. There-

fore the analog input must be stable for at least 2

m

sec

before and 1

m

sec after the eighth S

CLK

falling edge to

ensure a proper conversion. External input source resist-

ance and capacitance will lengthen the acquisition time and

should be accounted for.

Other conventional sample and hold error specifications are

included in the error and timing specs of the A/D. The hold

step and gain error sample/hold specs are taken into ac-

count in the ADC0811’s total unadjusted error, while the

hold settling time is included in the A/D’s max conversion

time of 64

w

2

clock periods. The hold droop rate can be

thought of as being zero since an unlimited amount of time

can pass between a conversion and the reading of data.

However, once the data is read it is lost and another conver-

sion is started.

Typical Applications

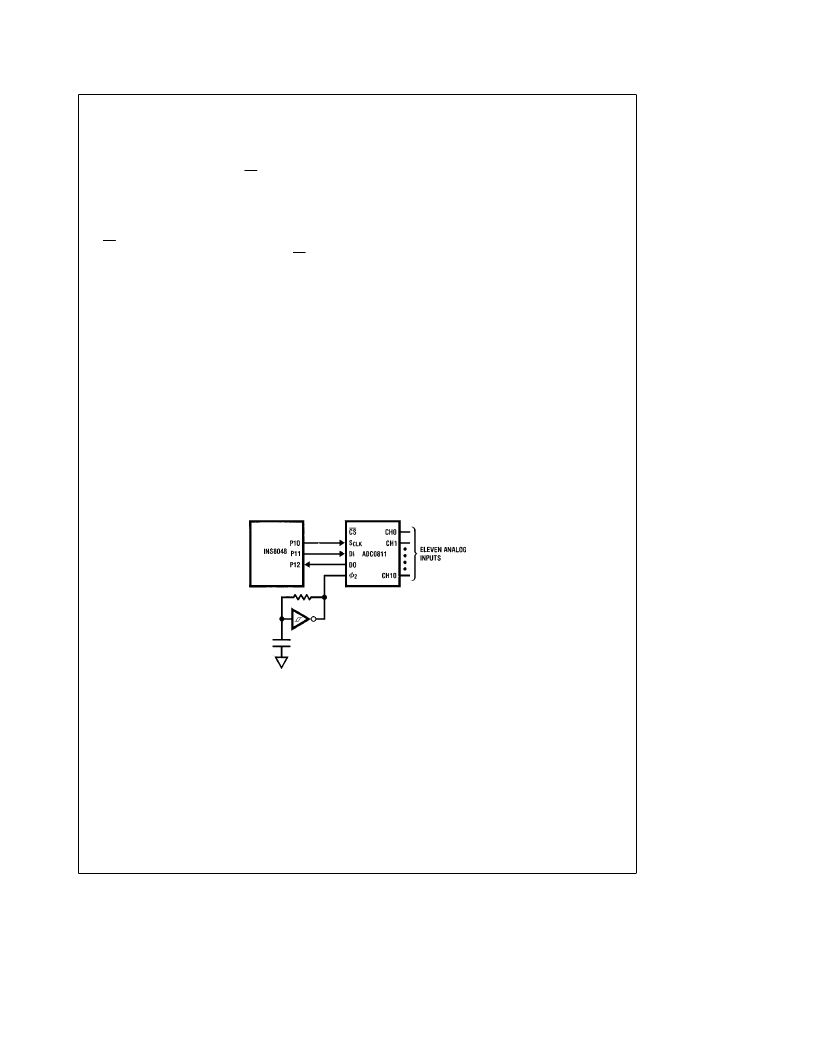

ADC0811-INS8048 INTERFACE

TL/H/5587–21

10

相关PDF资料 |

PDF描述 |

|---|---|

| ADC0811BCV | 8-Bit Serial I/O A/D Converter With 11-Channel Multiplexer |

| ADC0811CCJ | 8-Bit Serial I/O A/D Converter With 11-Channel Multiplexer |

| ADC0811CCN | 8-Bit Serial I/O A/D Converter With 11-Channel Multiplexer |

| ADC0811CCV | 8-Bit Serial I/O A/D Converter With 11-Channel Multiplexer |

| ADC08131CIWM | 8-Bit High-Speed Serial I/O A/D Converters with Multiplexer Options, Voltage Reference, and Track/Hold Function |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADC0811BCN/A+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 8-Bit |

| ADC0811BCN/B+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 8-Bit |

| ADC0811BCV | 制造商:NSC 制造商全称:National Semiconductor 功能描述:8-Bit Serial I/O A/D Converter With 11-Channel Multiplexer |

| ADC0811BJ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog-to-Digital Converter, 8-Bit |

| ADC0811CCJ | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。