- 您现在的位置:买卖IC网 > PDF目录10679 > ADCMP562BRQ (Analog Devices Inc)IC COMPARATOR PECL DUAL 20QSOP PDF资料下载

参数资料

| 型号: | ADCMP562BRQ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 13/16页 |

| 文件大小: | 0K |

| 描述: | IC COMPARATOR PECL DUAL 20QSOP |

| 标准包装: | 56 |

| 类型: | 带锁销 |

| 元件数: | 2 |

| 输出类型: | 补充型,差分,开路发射极,PECL |

| 电压 - 电源,单路/双路(±): | ±4.75 V ~ 5.25 V |

| 电压 - 输入偏移(最小值): | 2mV @ -5.2V,5V |

| 电流 - 输入偏压(最小值): | 3µA @ -5.2V,5V |

| 电流 - 输出(标准): | 30mA |

| 电流 - 静态(最大值): | 5mA,28mA,13mA |

| CMRR, PSRR(标准): | 80dB CMRR,85dB PSRR |

| 传输延迟(最大): | 0.83ns |

| 磁滞: | ±1mV |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 20-SSOP(0.154",3.90mm 宽) |

| 安装类型: | 表面贴装 |

| 包装: | 管件 |

| 配用: | EVAL-ADCMP562BRQZ-ND - BOARD EVALUATION ADCMP562BRQZ |

ADCMP561/ADCMP562

Rev. A | Page 6 of 16

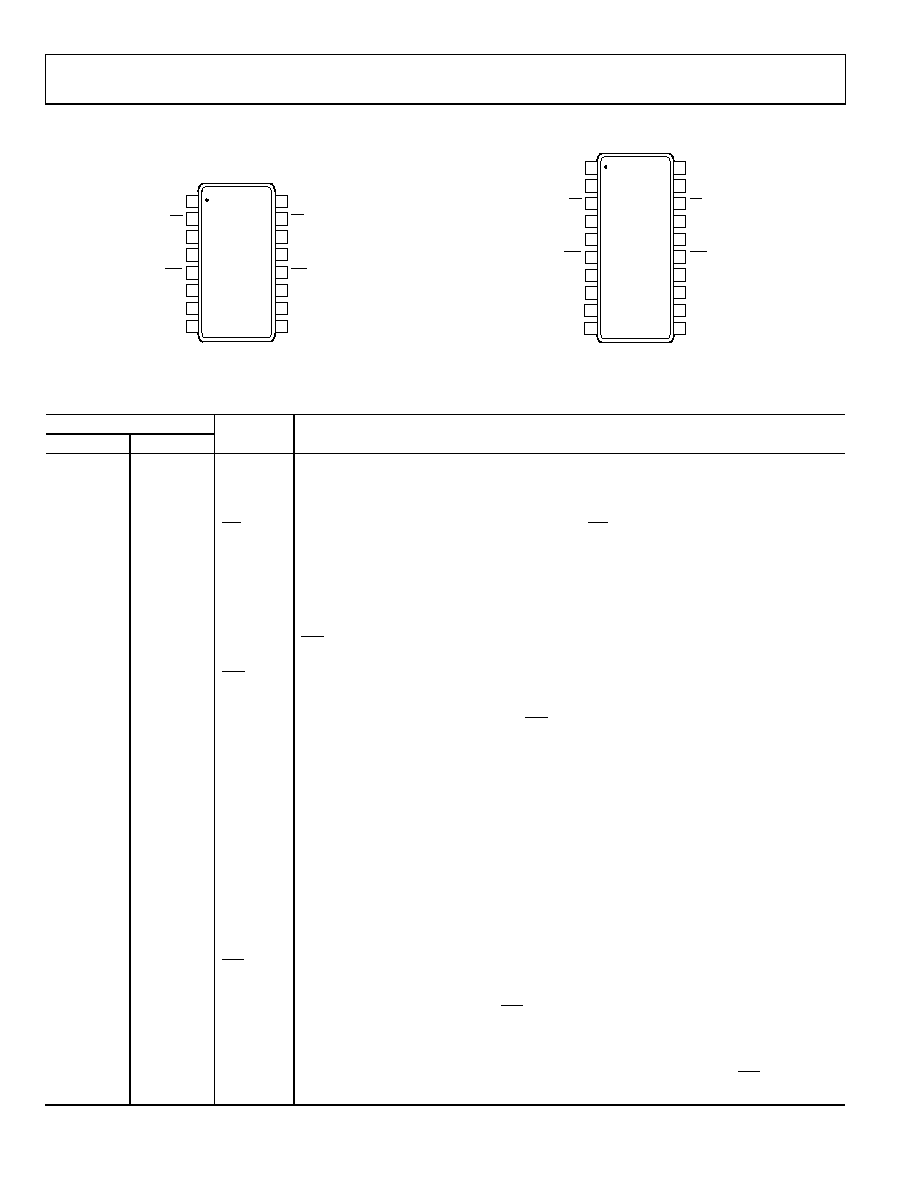

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

04687-0-002

ADCMP561

TOP VIEW

(Not to Scale)

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

–INA

+INA

QA

VDD

VEE

LEA

–INB

+INB

QB

GND

VCC

LEB

04687-0-003

ADCMP562

TOP VIEW

(Not to Scale)

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

–INA

QA

VDD

VEE

LEA

VDD

+INA

HYSA

–INB

QB

GND

VCC

LEB

VDD

+INB

HYSB

Figure 4. ADCMP561 16-Lead QSOP Pin Configuration

Figure 5. ADCMP562 20-Lead QSOP Pin Configuration

Table 3. Pin Function Descriptions

Pin No.

ADCMP561

ADCMP562

Mnemonic

Function

1

VDD

Logic Supply Terminal.

1

2

QA

One of two complementary outputs for Channel A. QA is logic high if the analog voltage at the

noninverting input is greater than the analog voltage at the inverting input (provided the

comparator is in compare mode). See the description of Pin LEA for more information.

2

3

QA

One of two complementary outputs for Channel A. QA is logic low if the analog voltage at the

noninverting input is greater than the analog voltage at the inverting input (provided the

comparator is in compare mode). See the description of Pin LEA for more information.

3

4

VDD

Logic Supply Terminal.

4

5

LEA

One of two complementary inputs for Channel A Latch Enable. In compare mode (logic high),

the output tracks changes at the input of the comparator. In the latch mode (logic low), the

output reflects the input state just prior to the comparator’s being placed in the latch mode.

LEA must be driven in conjunction with LEA. If left unconnected, the comparator defaults to

compare mode.

5

6

LEA

One of two complementary inputs for Channel A Latch Enable. In compare mode (logic low),

the output tracks changes at the input of the comparator. In latch mode (logic high), the

output reflects the input state just prior to the comparator’s being placed in the latch mode.

LEA must be driven in conjunction with LEA. If left unconnected, the comparator defaults to

compare mode.

6

7

VEE

Negative Supply Terminal.

7

8

INA

Inverting Analog Input of the Differential Input Stage for Channel A. The inverting A input must

be driven in conjunction with the noninverting A input.

8

9

+INA

Noninverting Analog Input of the Differential Input Stage for Channel A. The noninverting

A input must be driven in conjunction with the inverting A input.

10

HYSA

Programmable Hysteresis Input.

11

HYSB

Programmable Hysteresis Input.

9

12

+INB

Noninverting Analog Input of the Differential Input Stage for Channel B. The noninverting

B input must be driven in conjunction with the inverting B input.

10

13

INB

Inverting Analog Input of the Differential Input Stage for Channel B. The inverting B input must

be driven in conjunction with the noninverting B input.

11

14

VCC

Positive Supply Terminal.

12

15

LEB

One of two complementary inputs for Channel B Latch Enable. In compare mode (logic low),

the output tracks changes at the input of the comparator. In latch mode (logic high), the

output reflects the input state just prior to placing the comparator in the latch mode. LEB

must be driven in conjunction with LEB. If left unconnected, the comparator defaults to

compare mode.

13

16

LEB

One of two complementary inputs for Channel B Latch Enable. In compare mode (logic high),

the output tracks changes at the input of the comparator. In latch mode (logic low), the output

reflects the input state just prior to placing the comparator in the latch mode. LEB must be

driven in conjunction with LEB. If left unconnected, the comparator defaults to compare mode.

相关PDF资料 |

PDF描述 |

|---|---|

| ADCMP551BRQ | IC COMPARATOR PECL/LVPECL 16QSOP |

| AD790JR-REEL | IC COMPARATOR PREC W/LATCH 8SOIC |

| LT1016IS8 | IC COMPARATOR 10NS HI-SPD 8-SOIC |

| LT1721IGN#TR | IC COMP QUAD R-R 4.5NS 16SSOP |

| LT1721IGN | IC COMP R-RINOUT QUAD 16-SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADCMP562BRQZ | 功能描述:IC COMPARATOR PECL DUAL 20-QSOP RoHS:是 类别:集成电路 (IC) >> 线性 - 比较器 系列:- 标准包装:1 系列:- 类型:通用 元件数:1 输出类型:CMOS,开路集电极,TTL 电压 - 电源,单路/双路(±):2.7 V ~ 5.5 V 电压 - 输入偏移(最小值):7mV @ 5V 电流 - 输入偏压(最小值):0.25µA @ 5V 电流 - 输出(标准):84mA @ 5V 电流 - 静态(最大值):120µA CMRR, PSRR(标准):- 传输延迟(最大):600ns 磁滞:- 工作温度:-40°C ~ 85°C 封装/外壳:SC-74A,SOT-753 安装类型:表面贴装 包装:剪切带 (CT) 产品目录页面:1268 (CN2011-ZH PDF) 其它名称:*LMV331M5*LMV331M5/NOPBLMV331M5CT |

| ADCMP562BRQZ-RL7 | 功能描述:IC COMPARATOR PECL DUAL 20QSOP RoHS:是 类别:集成电路 (IC) >> 线性 - 比较器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:通用 元件数:1 输出类型:CMOS,推挽式,满摆幅,TTL 电压 - 电源,单路/双路(±):2.5 V ~ 5.5 V,±1.25 V ~ 2.75 V 电压 - 输入偏移(最小值):5mV @ 5.5V 电流 - 输入偏压(最小值):1pA @ 5.5V 电流 - 输出(标准):- 电流 - 静态(最大值):24µA CMRR, PSRR(标准):80dB CMRR,80dB PSRR 传输延迟(最大):450ns 磁滞:±3mV 工作温度:-40°C ~ 85°C 封装/外壳:6-WFBGA,CSPBGA 安装类型:表面贴装 包装:管件 其它名称:Q3554586 |

| ADCMP563 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual High Speed ECL Comparators |

| ADCMP563_05 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual, High Speed ECL Comparators |

| ADCMP563BCP-R2 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。