参数资料

| 型号: | ADF4156BCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 13/24页 |

| 文件大小: | 0K |

| 描述: | IC PLL FRAC-N FREQ SYNTH 20LFCSP |

| 产品变化通告: | Improve Phase Noise Performance |

| 设计资源: | Low-Noise Microwave fractional-N PLL using active loop filter and RF prescaler (CN0174) |

| 标准包装: | 1 |

| 类型: | 分数 N 合成器(RF) |

| PLL: | 是 |

| 输入: | CMOS,TTL |

| 输出: | 时钟 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:1 |

| 差分 - 输入:输出: | 是/无 |

| 频率 - 最大: | 6.2GHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 2.7 V ~ 3.3 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 20-LFCSP-VQ |

| 包装: | 托盘 |

| 产品目录页面: | 551 (CN2011-ZH PDF) |

ADF4156

Data Sheet

Rev. E | Page 20 of 24

PHASE RESYNC

The output of a fractional-N PLL can settle to any MOD phase

offset with respect to the input reference, where MOD is the

fractional modulus. The phase resync feature in the ADF4156 is

used to produce a consistent output phase offset with respect to

the input reference. This is necessary in applications where the

output phase and frequency are important, such as digital beam

forming. See the Phase Programmability section for information

about how to program a specific RF output phase when using

the phase resync feature.

Phase resync is enabled by setting Bits DB[20:19] in Register R4

to 10. When phase resync is enabled, an internal timer generates

sync signals at intervals of tSYNC as indicated by the following

formula:

tSYNC = CLK_DIV_VALUE × MOD × tPFD

where:

tPFD is the PFD reference period.

CLK_DIV_VALUE is the decimal value programmed in

Bit DB[18:7] of Register R4. This value can be any integer in the

range of 1 to 4095.

MOD is the modulus value programmed in Bit DB[14:3] of

Register R2.

When a new frequency is programmed, the second sync pulse

after the LE rising edge is used to resynchronize the output

phase to the reference. The tSYNC time should be programmed to

a value that is at least as long as the worst-case lock time. Doing

so guarantees that the phase resync occurs after the last cycle

slip in the PLL settling transient.

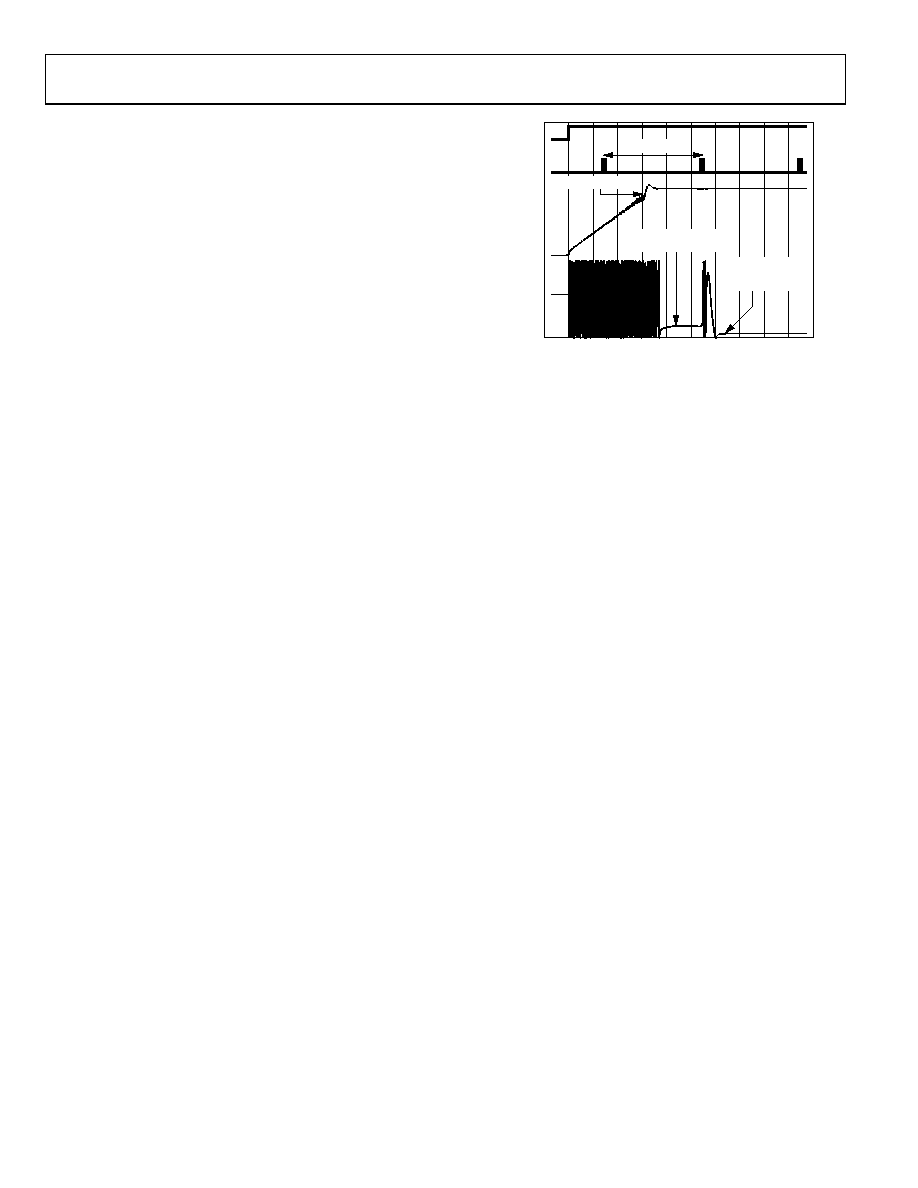

In the example shown in Figure 24, the PFD reference is

25 MHz and the MOD value is 125 for a 200 kHz channel

spacing. Therefore, tSYNC is set to 400 s by programming

CLK_DIV_VALUE to 80.

LE

PHASE

FREQUENCY

SYNC

(Internal)

–100

0

100

200

1000

300

400

500

600

700

800

900

05863-

016

TIME (s)

PLL SETTLES TO

CORRECT PHASE

AFTER RESYNC

tSYNC

LAST CYCLE SLIP

PLL SETTLES TO

INCORRECT PHASE

Figure 24. Phase Resync Example

Phase Programmability

To program a specific RF output phase, change the phase word

in Register R1. As this word is swept from 0 to MOD, the RF output

phase sweeps over a 360o/MOD range in steps of 360o/MOD.

LOW FREQUENCY APPLICATIONS

The specification on the RF input is 0.5 GHz minimum; however,

lower RF frequencies can be used if the minimum slew rate

specification of 400 V/s is met. An appropriate LVDS driver, such

as the FIN1001 from Fairchild Semiconductor, can be used to

square up the RF signal before it is fed back into the ADF4156

RF input.

FILTER DESIGN—ADIsimPLL

A filter design and analysis program is available to help implement

the PLL design. Visit www.analog.com/pll for a free download

of the ADIsimPLL software. This software designs, simulates,

and analyzes the entire PLL frequency domain and time domain

response. Various passive and active filter architectures are allowed.

When designing the loop filter, keep the ratio of the PFD frequency

to the loop bandwidth >200:1 to attenuate the Σ-Δ modulator noise.

相关PDF资料 |

PDF描述 |

|---|---|

| X9317UV8Z-2.7 | IC XDCP 100TAP 50K 3-WIRE 8TSSOP |

| ISPPAC-CLK5320S-01TN64I | IC BUFFER FANOUT 20OUTPUT 64TQFP |

| VE-J10-MZ-S | CONVERTER MOD DC/DC 5V 25W |

| SY100S838LZG | IC CLOCK GEN 3.3V/5V 20-SOIC |

| X9317UM8Z-2.7 | IC XDCP 100TAP 10K 3-WIRE 8-MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADF4156BCPZ-RL | 功能描述:IC PLL FRAC-N FREQ SYNTH 20LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| ADF4156BCPZ-RL7 | 功能描述:IC PLL FRAC-N FREQ SYNTH 20LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| ADF4156BCPZ-U1 | 制造商:Analog Devices 功能描述:FRACTIONAL-N SYNTH. W/FASTLOCK COUNTER - Trays |

| ADF4156BRUZ | 功能描述:IC PLL FRAC-N FREQ SYNTH 16TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

| ADF4156BRUZ-RL | 功能描述:IC PLL FRAC-N FREQ SYNTH 16TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

发布紧急采购,3分钟左右您将得到回复。