参数资料

| 型号: | ADF4156BCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 8/24页 |

| 文件大小: | 0K |

| 描述: | IC PLL FRAC-N FREQ SYNTH 20LFCSP |

| 产品变化通告: | Improve Phase Noise Performance |

| 设计资源: | Low-Noise Microwave fractional-N PLL using active loop filter and RF prescaler (CN0174) |

| 标准包装: | 1 |

| 类型: | 分数 N 合成器(RF) |

| PLL: | 是 |

| 输入: | CMOS,TTL |

| 输出: | 时钟 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:1 |

| 差分 - 输入:输出: | 是/无 |

| 频率 - 最大: | 6.2GHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 2.7 V ~ 3.3 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 20-LFCSP-VQ |

| 包装: | 托盘 |

| 产品目录页面: | 551 (CN2011-ZH PDF) |

ADF4156

Data Sheet

Rev. E | Page 16 of 24

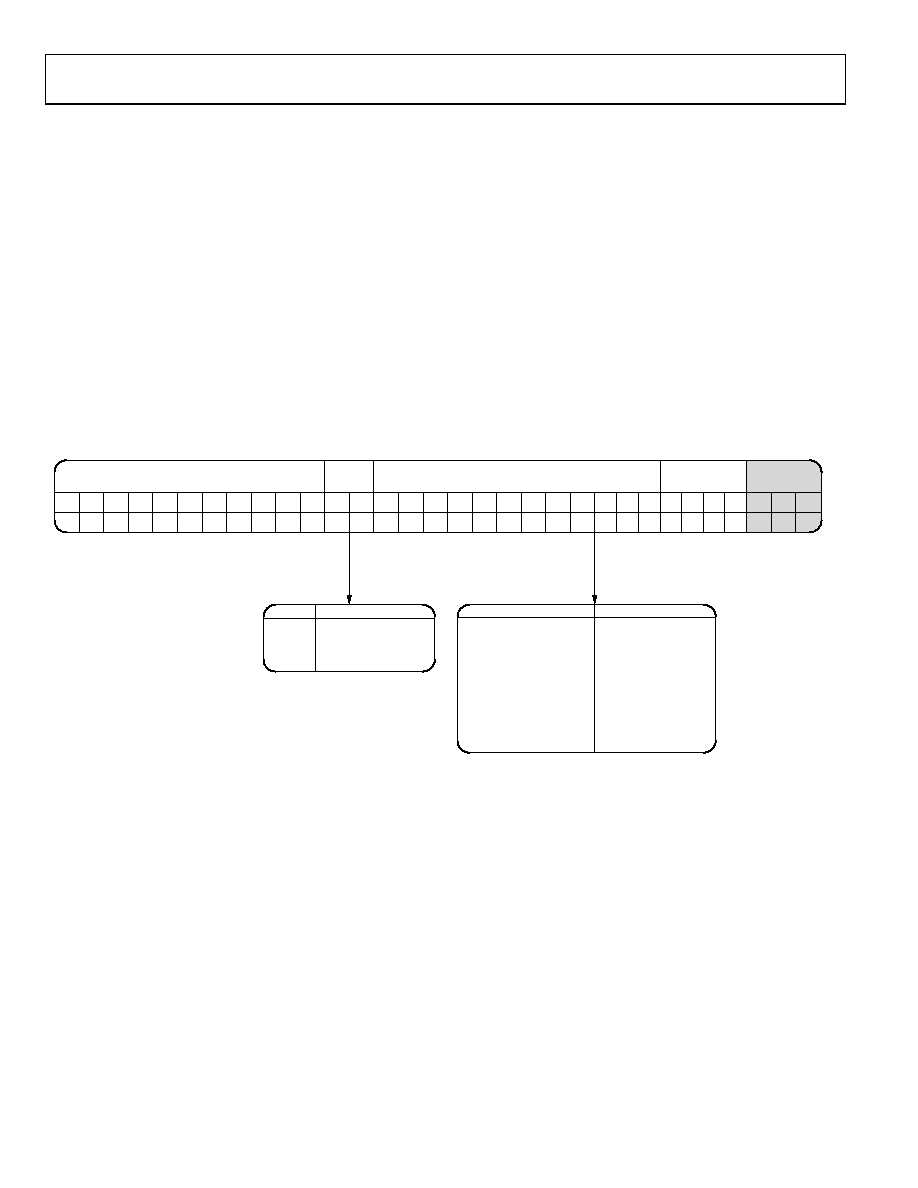

CLK DIV REGISTER, R4

With the control bits (Bits[2:0]) of Register R3 set to 100, the

on-chip clock divider register (R4) is programmed. Figure 21

shows the input data format for programming this register.

12-Bit Clock Divider Value

The 12-bit clock divider value sets the timeout counter for

activation of the fast-lock mode or a phase resync. See the Phase

Resync section for more information.

Clock Divider Mode

DB[20:19] control the mode of the clock divider in the ADF4156.

These bits should be set to 01 to activate the fast-lock mode, or

to 10 to activate a phase resync. In most applications, neither a

fast lock nor a phase resync is required. In this case, DB[20:19]

should be set to 00.

RESERVED BITS

All reserved bits should be set to 0 for normal operation.

INITIALIZATION SEQUENCE

After powering up the part, the correct register programming

sequence is as follows:

1. CLK DIV register (R4)

2. Function register (R3)

3. MOD/R register (R2)

4. Phase register (R1)

5. FRAC/INT register (R0)

DB31 DB30 DB29 DB28 DB27 DB26 DB25 DB24 DB23 DB22 DB21 DB20 DB19 DB18 DB17 DB16 DB15 DB14 DB13 DB12 DB11 DB10 DB9 DB8 DB7 DB6 DB5 DB4 DB3 DB2

DB1

DB0

0

M2

M1

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

R4

R3

R2

R1

C3(1) C2(0) C1(0)

CONTROL

BITS

RESERVED

CLK

DIV

MODE

12-BIT CLOCK DIVIDER VALUE

M2

M1

CLK DIV MODE

0

CLK DIV OFF

0

1

FAST-LOCK MODE

1

0

RESYNC TIMER ENABLED

1

RESERVED

D12

D11

.......... D2

D1

CLOCK DIVIDER VALUE

0

.......... 0

0

.......... 0

1

0

.......... 1

0

2

0

.......... 1

1

3

.

.......... .

.

.......... .

.

.......... .

.

1

.......... 0

0

4092

1

.......... 0

1

4093

1

.......... 1

0

4094

1

.......... 1

1

4095

05863-

015

Figure 21. CLK DIV Register (R4) Map

相关PDF资料 |

PDF描述 |

|---|---|

| X9317UV8Z-2.7 | IC XDCP 100TAP 50K 3-WIRE 8TSSOP |

| ISPPAC-CLK5320S-01TN64I | IC BUFFER FANOUT 20OUTPUT 64TQFP |

| VE-J10-MZ-S | CONVERTER MOD DC/DC 5V 25W |

| SY100S838LZG | IC CLOCK GEN 3.3V/5V 20-SOIC |

| X9317UM8Z-2.7 | IC XDCP 100TAP 10K 3-WIRE 8-MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADF4156BCPZ-RL | 功能描述:IC PLL FRAC-N FREQ SYNTH 20LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| ADF4156BCPZ-RL7 | 功能描述:IC PLL FRAC-N FREQ SYNTH 20LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| ADF4156BCPZ-U1 | 制造商:Analog Devices 功能描述:FRACTIONAL-N SYNTH. W/FASTLOCK COUNTER - Trays |

| ADF4156BRUZ | 功能描述:IC PLL FRAC-N FREQ SYNTH 16TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

| ADF4156BRUZ-RL | 功能描述:IC PLL FRAC-N FREQ SYNTH 16TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

发布紧急采购,3分钟左右您将得到回复。