参数资料

| 型号: | ADN2806ACPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 20/20页 |

| 文件大小: | 0K |

| 描述: | IC CLK/DATA REC 622MBPS 32-LFCSP |

| 标准包装: | 1 |

| 类型: | 时钟和数据恢复(CDR),多路复用器 |

| PLL: | 是 |

| 主要目的: | SONET/SDH |

| 输入: | CML |

| 输出: | LVDS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 622MHz |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 托盘 |

ADN2806

Rev. C | Page 9 of 20

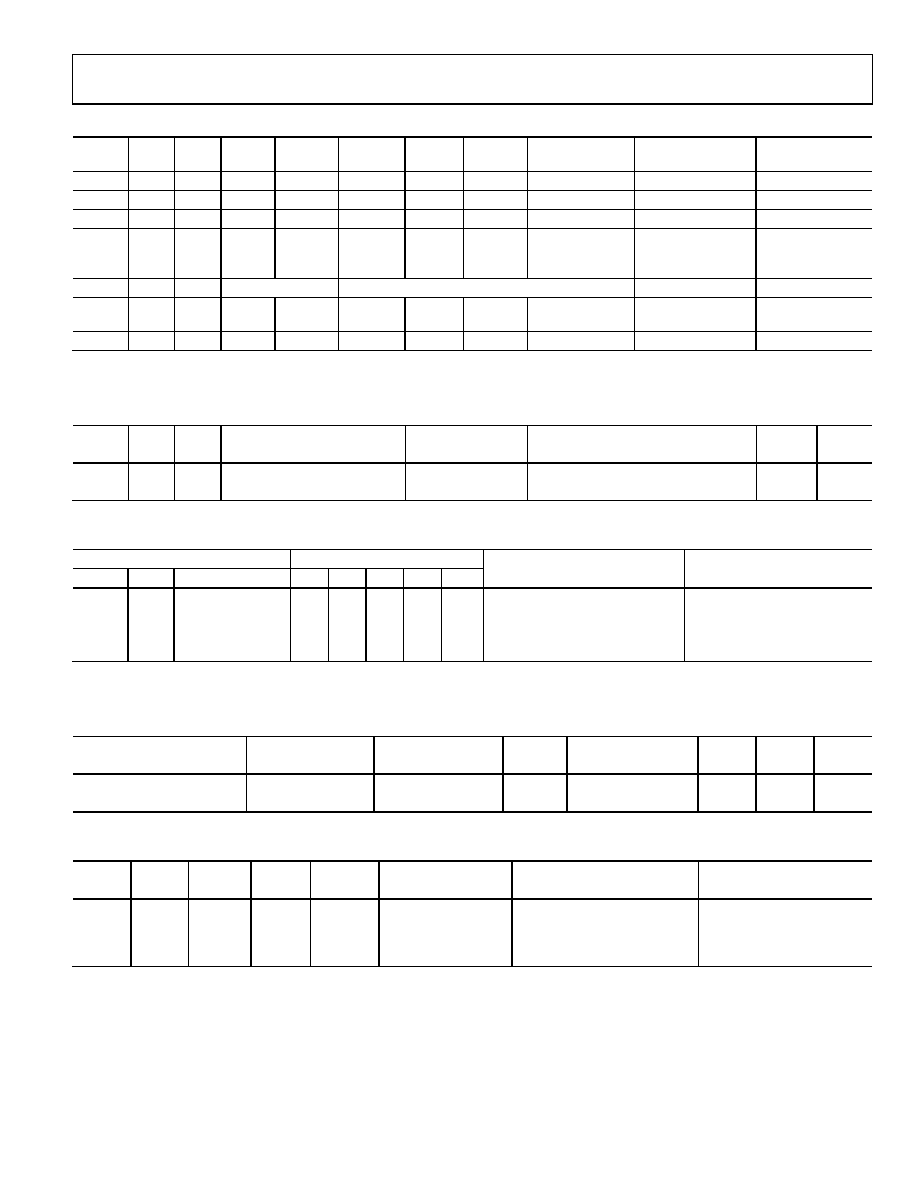

Reg

Name

R/W

Addr

D7

D6

D5

D4

D3

D2

D1

D0

FREQ0

R

0x0

MSB

LSB

FREQ1

R

0x1

MSB

LSB

FREQ2

R

0x2

0

MSB

LSB

MISC

R

0x4

x

LOS

status

Static

LOL

status

Data rate

measurement

complete

x

CTRLA

W

0x8

FREF range

Data rate/DIV_FREF ratio

Measure data rate

Lock to reference

CTRLB

W

0x9

Config

LOL

Reset

MISC[4]

System

reset

0

Reset

MISC[2]

0

CTRLC

W

0x11

0

Config LOS

SQUELCH mode

0

1 All writeable registers default to 0x00.

Table 7. Miscellaneous Register, MISC

Static LOL

LOL Status

Data Rate Measurement Complete

D7

D6

D5

D4

D3

D2

D1

D0

x

0 = Waiting for next LOL

0 = Locked

0 = Measuring data rate

x

1 = Static LOL until reset

1 = Acquiring

1 = Measurement complete

FREF Range

Data Rate/Div_FREF Ratio

Measure Data Rate

Lock to Reference

D7

D6

D5

D4

D3

D2

D1

D0

0

19.44 MHz

0

1

0

1

32

Set to 1 to measure data rate

0 = Lock to input data

0

1

38.88 MHz

0

1

0

1

32

1 = Lock to reference clock

1

0

77.76 MHz

0

1

0

1

32

1

155.52 MHz

0

1

0

1

32

1 Where DIV_F

REF

is the divided down reference referred to the 10 MHz to 20 MHz band (see the R

section).

Table 9. Control Register, CTRLB

Config LOL

Reset MISC[4]

System Reset

Reset MISC[2]

D7

D6

D5

D4

D3

D2

D1

D0

0 = LOL pin normal operation

1 = LOL pin is static LOL

Write a 1 followed

by 0 to reset MISC[4]

Write a 1 followed by

0 to reset ADN2806

Set to 0

Write a 1 followed

by 0 to reset MISC[2]

Set to 0

Table 10. Control Register, CTRLC

Config LOS

SQUELCH Mode

Output Boost

D7

D6

D5

D4

D3

D2

D1

D0

Set to 0

0 = Active high LOS

1 = Active low LOS

0 = Squelch data outputs and

clock outputs

1 = Squelch data outputs or

clock outputs

0 (Default output swing)

相关PDF资料 |

PDF描述 |

|---|---|

| ADN2807ACPZ | IC CLOCK/DATA RECOVERY 48LFCSP |

| ADN2811ACPZ-CML | IC CLK/DATA REC W/AMP 48-LFCSP |

| ADN2812ACPZ-RL7 | IC CLOCK/DATA RECOVERY 32LFCSP |

| ADN2813ACPZ-500RL7 | IC CLK/DATA REC 1.25GBPS 32LFCSP |

| ADN2814ACPZ-500RL7 | IC CLK/DATA REC 675MBPS 32-LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADN2806ACPZ-500RL7 | 功能描述:IC CLK/DATA REC 622MBPS 32-LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ADN2806ACPZ-RL7 | 功能描述:IC CLK/DATA REC 622MBPS 32-LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ADN2807 | 制造商:AD 制造商全称:Analog Devices 功能描述:155/622 Mb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2807ACP | 制造商:Analog Devices 功能描述:CDR 155.52Mbps/166.63Mbps/622.08Mbps/666.51Mbps SONET/SDH 48-Pin LFCSP EP Tray |

| ADN2807ACP-RL | 制造商:AD 制造商全称:Analog Devices 功能描述:155/622 Mb/s Clock and Data Recovery IC with Integrated Limiting Amp |

发布紧急采购,3分钟左右您将得到回复。