参数资料

| 型号: | ADN2818ACPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 24/40页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK/DATA RECOVERY 32-LFCSP |

| 标准包装: | 1 |

| 类型: | 时钟和数据恢复(CDR),多路复用器 |

| PLL: | 是 |

| 主要目的: | SONET/SDH |

| 输入: | CML |

| 输出: | CML |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 2.7GHz |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ(5x5) |

| 包装: | 托盘 |

| 产品目录页面: | 788 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

ADN2817/ADN2818

Data Sheet

Rev. E | Page 30 of 40

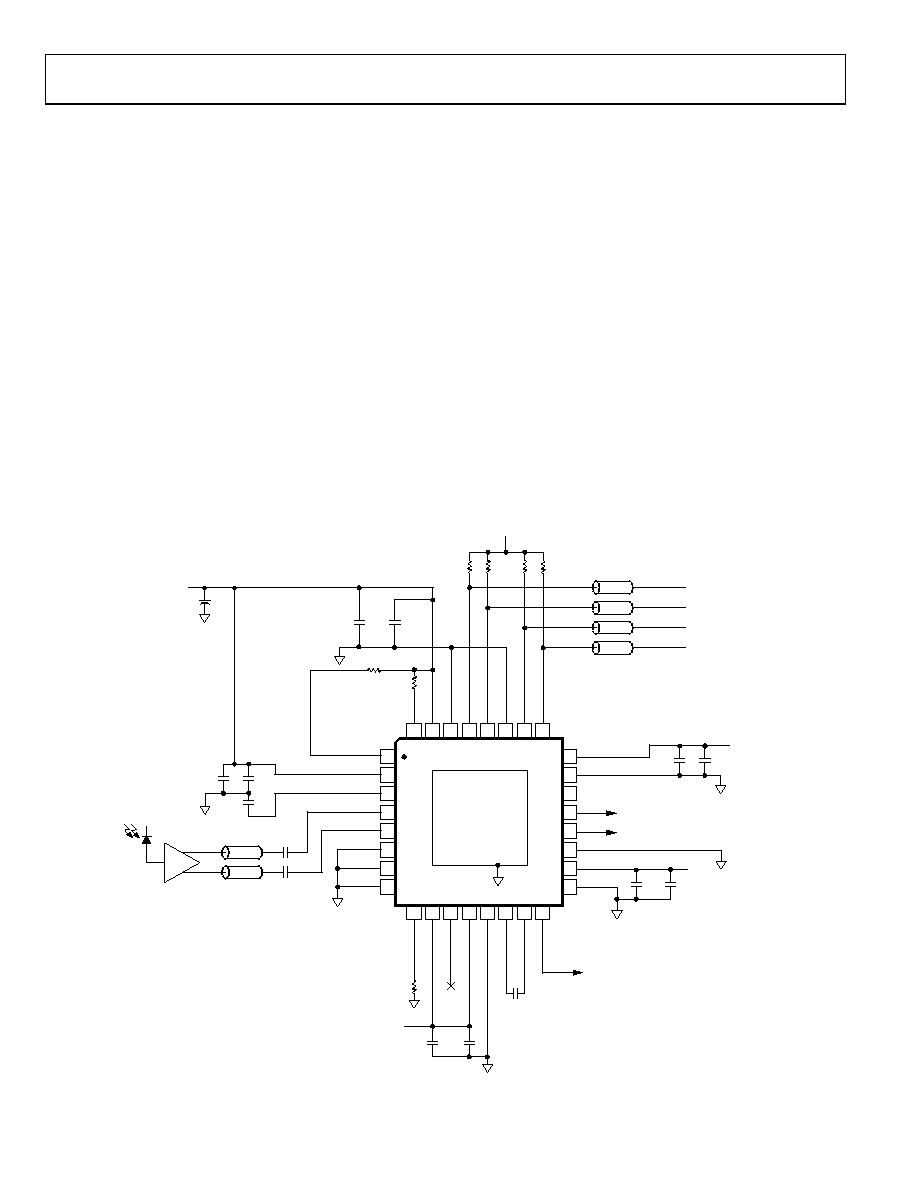

APPLICATIONS INFORMATION

PCB DESIGN GUIDELINES

Proper RF PCB design techniques must be used for optimal

performance.

Power Supply Connections and Ground Planes

For best practice, the use of one low impedance ground plane is

recommended. To reduce series inductance, solder the VEE pins

directly to the ground plane. If the ground plane is an internal

plane and connections to the ground plane are made through

vias, multiple vias can be used in parallel to reduce the series

inductance, especially on Pin 23, which is the ground return for

the output buffers. Connect the exposed pad to the ground

plane using plugged vias so that solder does not leak through

the vias during reflow.

Use of a 10 F electrolytic capacitor between VCC and VEE is

recommended at the location where the 3.3 V supply enters the

PCB. When using 0.1 F and 1 nF ceramic chip capacitors, they

should be placed between the IC power supply (VCC and VEE),

as close as possible to the ADN2817/ADN2818 VCC pins.

If connections to the supply and ground are made through

vias, the use of multiple vias in parallel helps to reduce series

inductance, especially on Pin 24, which supplies power to the

high speed CLKOUTP/CLKOUTN and DATAOUTP/DATAOUTN

output buffers. See the schematic in Figure 36 for recommended

connections.

By using adjacent power supply and ground planes, excellent

high frequency decoupling can be realized by using close

spacing between the planes. This capacitance is given by

CPLANE = 0.88εr A/d (pF)

where:

εr is the dielectric constant of the PCB material.

A is the area of the overlap of power and ground planes (cm2).

d is the separation between planes (mm).

For FR-4, εr = 4.4 and 0.25 mm spacing, C ≈ 15 pF/cm2.

VB

ER

32

V

CC

31

VEE

30

DAT

AO

UT

P

29

DAT

AO

UT

N

28

S

Q

UE

L

CH

27

CL

KO

UT

P

26

CL

KO

UT

N

25

T

HRADJ

RTH

9

RE

F

CL

KP

10

RE

F

CL

KN

11

V

CC

12

VEE

13

CF

2

14

CF

1

15

LOL

16

BERMODE

1

VCC

2

VREF

3

NIN

4

PIN

5

SLICEP

6

SLICEN

7

VEE

8

VCC

24

VEE

23

LOS

22

SDA

21

SCK

EXPOSED PAD

TIED OFF TO VEE

PLANE WITH VIAS.

20

SADDR5

19

VCC

18

VEE

17

ADN2817/

ADN2818

TOP VIEW

(Not to Scale)

1nF

0.1F

VCC

0.47F +20%

>300M

INSULATION RESISTANCE

C

I2C CONTROLLER

C

VCC

1nF

0.1F

1nF

0.1F

CIN

VCC

TIA

50

1nF

0.1F

DATAOUTP

DATAOUTN

CLKOUTP

CLKOUTN

50 TRANSMISSION

LINES

VCC

4 × 100

1nF

0.1F

+

VCC

10F

06001-

025

10k

10k

Figure 36. Typical ADN2817/ADN2818 Applications Circuit

相关PDF资料 |

PDF描述 |

|---|---|

| XRT91L31IQ-F | IC TXRX SONET/SDH 8BIT 64QFP |

| MS27496E19A32S | CONN RCPT 32POS BOX MNT W/SCKT |

| AD9548BCPZ | IC CLOCK GEN/SYNCHRONIZR 88LFCSP |

| V375C36M150BL3 | CONVERTER MOD DC/DC 36V 150W |

| MAX3676EHJ+ | IC CLOCK RECOVERY 32-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADN2818ACPZ-RL | 制造商:AD 制造商全称:Analog Devices 功能描述:Continuous Rate 10 Mbps to 2.7 Gbps Clock and Data Recovery ICs |

| ADN2818ACPZ-RL7 | 功能描述:IC CLOCK/DATA RECOVERY 32-LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ADN2819 | 制造商:AD 制造商全称:Analog Devices 功能描述:Multirate to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2819ACP-CML | 制造商:Analog Devices 功能描述:CDR 2488.32Mbps/2666.06Mbps SONET/SDH 48-Pin LFCSP EP Tray 制造商:Rochester Electronics LLC 功能描述:MULTI-RATE 2.7GBPS CDR/ PA LOW POWER I.C - Bulk |

| ADN2819ACP-CML-RL | 制造商:Analog Devices 功能描述:CDR 2488.32Mbps/2666.06Mbps SONET/SDH 48-Pin LFCSP EP T/R |

发布紧急采购,3分钟左右您将得到回复。