- 您现在的位置:买卖IC网 > PDF目录10710 > ADS1259BIPW (Texas Instruments)IC ADC 24BIT 14KSPS LN 20TSSOP PDF资料下载

参数资料

| 型号: | ADS1259BIPW |

| 厂商: | Texas Instruments |

| 文件页数: | 24/48页 |

| 文件大小: | 0K |

| 描述: | IC ADC 24BIT 14KSPS LN 20TSSOP |

| 产品培训模块: | Industrial Automation Overview |

| 标准包装: | 70 |

| 位数: | 24 |

| 采样率(每秒): | 14k |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 1 |

| 电压电源: | 模拟和数字,双 ± |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 20-TSSOP |

| 包装: | 管件 |

| 输入数目和类型: | 2 个单端,单极;2 个单端,双极;1 个差分,单极;1 个差分,双极 |

| 其它名称: | 296-27183-5 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

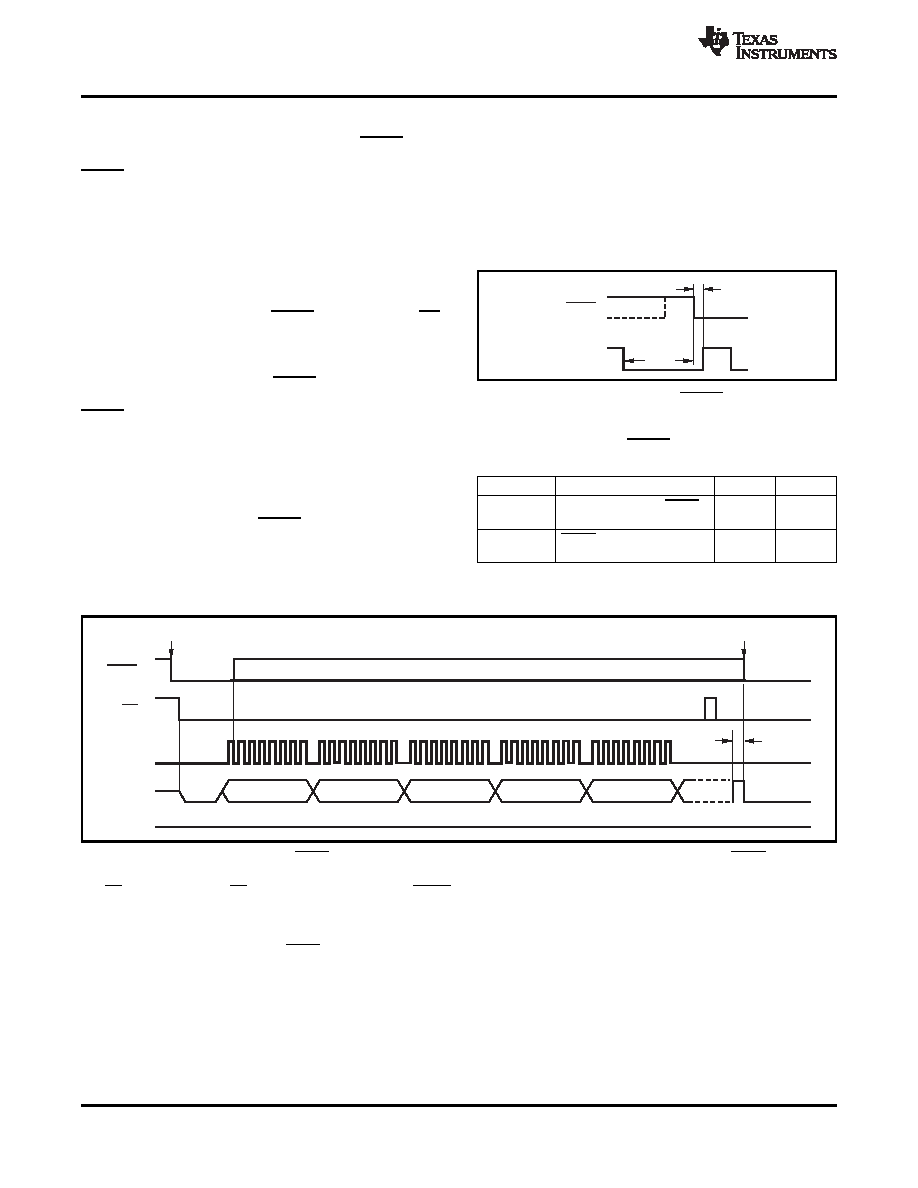

SCLK

DRDY

t

DRSC

t

SCDR

1

9

17

25

33

DRDY

(1)

CS

(2)

SCLK

(3)

DOUT

DATAMSB

DATAMID

DATALSB

CHECKSUM

(6)

DATAMSB

(7)

DIN

(8)

DataReady

NextDataReady

t

UPDATE

(4)

Hi-Z

(5)

SBAS424D

– JUNE 2009 – REVISED AUGUST 2011

DATA RETRIEVAL

The Read Data Continuous mode is cancelled by

sending the Stop Read Data Continuous command

New conversion data are available when DRDY goes

(SDATAC). This operation occurs simultaneously with

low. Read the data within 20 fCLK cycles of the next

ADC conversion data on DOUT which can be

DRDY falling edge or the data are incorrect. Do not

ignored. Once the SDATAC command is sent, other

read data during this interval. The conversion data

commands may be sent to the ADS1259. Observe

may be read in two ways: Data Read in Continuous

the SCLK and DRDY timing requirements, when

mode and Data Read in Stop Continuous mode.

reading data in this mode, as shown in Figure 59 and

Data Read Operation in Continuous Mode

In Read Data Continuous mode the conversion data

may be shifted out directly without the need of the

data read command. When DRDY (and DOUT, if CS

is low) assert low, the conversion data are ready. The

data are shifted out on DOUT on the rising edges of

SCLK, with the most significant bit (MSB) clocked out

first. In Gate Convert Mode, DRDY returns to high on

Figure 59. SCLK to DRDY Timing

the first falling edge of SCLK. In Pulse Convert mode,

DRDY remains low until a new conversion starts.

As shown in Figure 60, the conversion data consist of

Table 18. SCLK and DRDY Timing Characteristics

three or four bytes (data MSB first), depending on

for Figure 57

whether the checksum byte is included. The data

SYMBOL

DESCRIPTION

MIN

UNIT

may be read multiple times by continuing to shift the

tSCDR

SCLK low before DRDY

data. The data read operation must be completed

20

tCLK

low(1)

with 20 fCLK cycles of next DRDY falling edge.

tDRSC

DRDY falling edge to SCLK

40

ns

rising edge(1)

(1) These requirements apply only to reading conversion data in

RDATAC mode.

(1) In Gate Convert Conversion mode, DRDY returns to high on the first falling edge of SCLK. In Pulse Convert mode, DRDY remains low

until the next conversion is started.

(2) CS may be held low. If CS is low, DOUT asserts low with DRDY.

(3) Data are updated on the rising edge of SCLK. DOUT is low until the first rising edge of SCLK.

(4) tUPDATE = 20/fCLK. Do not read data during this time.

(5) During this interval, DOUT follows DRDY.

(6) Optional data checksum byte.

(7) Optional repeat of previous conversion data.

(8) Hold DIN low, except for transmission of the SDATAC (STOP Read Data Continuous command).

Figure 60. Data Read Operation in Continuous Mode

30

Copyright

2009–2011, Texas Instruments Incorporated

相关PDF资料 |

PDF描述 |

|---|---|

| TLC2551ID | IC 12BIT 400 KSPS ADC S/O 8-SOIC |

| MCP6544T-I/SL | IC COMP PUSHPULL 1.6V QUAD14SOIC |

| MCP6549T-I/SL | IC COMP OPENDRN 1.6V QUAD 14SOIC |

| MCP6549T-I/ST | IC COMP OPENDRN 1.6V QUAD14TSSOP |

| VI-2WX-IX-B1 | CONVERTER MOD DC/DC 5.2V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADS1259BIPW | 制造商:Texas Instruments 功能描述:A/D CONVERTER (A-D) IC |

| ADS1259BIPWR | 功能描述:模数转换器 - ADC Low-Noise 14kSPS 24B ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| ADS1259EVM | 功能描述:数据转换 IC 开发工具 ADS1259 Eval Mod RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| ADS1259EVM | 制造商:Texas Instruments 功能描述:DEVELOPMENT TOOL |

| ADS1259EVM-PDK | 功能描述:数据转换 IC 开发工具 ADS1259 Perf Demo Kit RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

发布紧急采购,3分钟左右您将得到回复。