- 您现在的位置:买卖IC网 > PDF目录10372 > ADS7825UG4 (Texas Instruments)IC 16BIT 4-CHAN MUX ADC 28-SOIC PDF资料下载

参数资料

| 型号: | ADS7825UG4 |

| 厂商: | Texas Instruments |

| 文件页数: | 4/21页 |

| 文件大小: | 0K |

| 描述: | IC 16BIT 4-CHAN MUX ADC 28-SOIC |

| 产品培训模块: | Data Converter Basics |

| 标准包装: | 20 |

| 位数: | 16 |

| 采样率(每秒): | 40k |

| 数据接口: | 串行,并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 50mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 28-SOIC |

| 包装: | 管件 |

| 输入数目和类型: | 4 个单端,双极 |

12

ADS7825

after the start of conversion ‘n’. Do not attempt to read data

beyond 12

s after the start of conversion ‘n’ until BUSY

(pin 24) goes HIGH; this may result in reading invalid data.

Refer to Table II and Figures 2 and 3 for timing constraints.

SERIAL OUTPUT

When PAR/SER (pin 20) is LOW, data can be clocked out

serially with the internal data clock or an external data clock.

When EXT/INT (pin 12) is LOW, DATACLK (pin 15) is an

output and is always active regardless of the state of CS (pin

23) and R/C (pin 22). The SDATA output is active when

BUSY (pin 24) is LOW. Otherwise, it is in a tri-state

condition. When EXT/INT is HIGH, DATACLK is an input.

The SDATA output is active when CS is LOW and R/C is

HIGH. Otherwise, it is in a tri-state condition. Regardless of

the state of EXT/INT, SYNC (pin 13) is an output and always

active, while TAG (pin 17) is always an input.

INTERNAL DATA CLOCK (During A Conversion)

To use the internal data clock, tie EXT/INT (pin 12) LOW.

The combination of R/C (pin 22) and CS (pin 23) LOW will

initiate conversion ‘n’ and activate the internal data clock

(typically 900kHz clock rate). The ADS7825 will output 16

bits of valid data, MSB first, from conversion ‘n – 1’ on

SDATA (pin 16), synchronized to 16 clock pulses output on

READING DATA

PARALLEL OUTPUT

To use the parallel output, tie PAR/SER (pin 20) HIGH. The

parallel output will be active when R/C (pin 22) is HIGH and

CS (pin 23) is LOW. Any other combination of CS and R/C

will tri-state the parallel output. Valid conversion data can be

read in two 8-bit bytes on D7-D0 (pins 9-13 and 15-17). When

BYTE (pin 21) is LOW, the 8 most significant bits will be

valid with the MSB on D7. When BYTE is HIGH, the 8 least

significant bits will be valid with the LSB on D0. BYTE can

be toggled to read both bytes within one conversion cycle.

Upon initial power up, the parallel output will contain

indeterminate data.

PARALLEL OUTPUT (After a Conversion)

After conversion ‘n’ is completed and the output registers

have been updated, BUSY (pin 24) will go HIGH. Valid data

from conversion ‘n’ will be available on D7-D0 (pins 9-13

and 15-17). BUSY going HIGH can be used to latch the

data. Refer to Table II and Figures 2 and 3 for timing

constraints.

PARALLEL OUTPUT (During a Conversion)

After conversion ‘n’ has been initiated, valid data from

conversion ‘n – 1’ can be read and will be valid up to 12

s

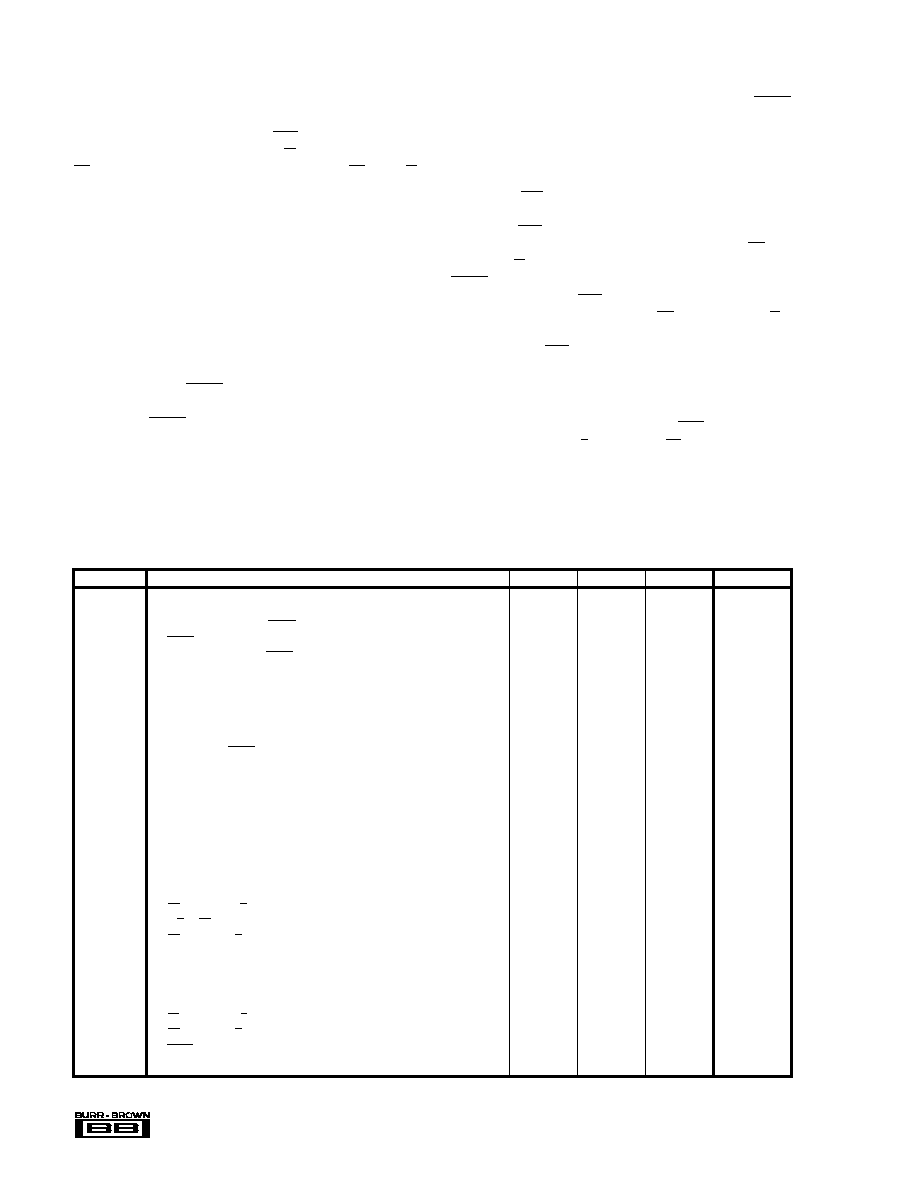

TABLE II. Conversion, Data, and Address Timing. TA = –40°C to +85°C.

SYMBOL

DESCRIPTION

MIN

TYP

MAX

UNITS

t1

Convert Pulse Width

0.04

12

s

t2

Start of Conversion to New Data Valid

20

21

s

t3

Start of Conversion to BUSY LOW

85

ns

t4

BUSY LOW

20

21

s

t5

End of Conversion to BUSY HIGH

90

ns

t6

Aperture Delay

40

ns

t7

Conversion Time

20

21

s

t8

Acquisition Time

45

s

t7 + t8

Throughput Time

25

s

t9

Bus Relinquish Time

10

83

ns

t10

Data Valid to BUSY HIGH

20

60

ns

t11

Start of Conversion to Previous Data Not Valid

12

20

s

t12

Bus Access Time and BYTE Delay

83

ns

t13

Start of Conversion to DATACLK Delay

1.4

s

t14

DATACLK Period

1.1

s

t15

Data Valid to DATACLK HIGH

20

75

ns

t16

DATACLK LOW to Data Not Valid

400

600

ns

t17

External DATACLK Period

100

ns

t18

External DATACLK HIGH

50

ns

t19

External DATACLK LOW

40

ns

t20

CS LOW and R/C HIGH to External DATACLK HIGH (Enable Clock)

25

ns

t21

R/C to CS Setup Time

10

ns

t22

CS HIGH or R/C LOW to External DATACLK HIGH (Disable Clock)

25

ns

t23

DATACLK HIGH to SYNC HIGH

15

35

ns

t24

DATACLK HIGH to Valid Data

25

55

ns

t25

Start of Conversion to SDATA Active

83

ns

t26

End of Conversion to SDATA Tri-State

83

ns

t27

CS LOW and R/C HIGH to SDATA Active

83

ns

t28

CS HIGH or R/C LOW to SDATA Tri-State

83

ns

t29

BUSY HIGH to Address Valid

20

ns

t30

Address Valid to BUSY LOW

500

ns

相关PDF资料 |

PDF描述 |

|---|---|

| D38999/20JD5AN | CONN HSG RCPT 5POS WALL MT PINS |

| D38999/20WB98SNLC | CONN HSG RCPT 6POS WALL MT SCKT |

| ADS7825UE4 | IC 16BIT 4-CHAN MUX ADC 28-SOIC |

| MS27473E8F98PLC | CONN HSG PLUG 3POS STRGHT PINS |

| MS27484T16B35SLC | CONN HSG PLUG 55POS STRGHT SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADS7826 | 制造商:TI 制造商全称:Texas Instruments 功能描述:10/8/12-BIT HIGH SPEED 2.7 V microPOWER SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| ADS7826EVM | 功能描述:数据转换 IC 开发工具 ADS7826 Eval Mod RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| ADS7826I | 制造商:TI 制造商全称:Texas Instruments 功能描述:10/8/12-BIT HIGH SPEED 2.7 V microPOWER SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| ADS7826IDRBR | 功能描述:模数转换器 - ADC 5.25V-2.7V 10 bit 200KSPS Synch Serial RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| ADS7826IDRBRG4 | 功能描述:模数转换器 - ADC 5.25V-2.7V 10 bit 200KSPS Synch Serial RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。