- 您现在的位置:买卖IC网 > PDF目录2065 > ADS8364Y/250G4 (Texas Instruments)IC ADC LP 16BIT 250KSPS 64-TQFP PDF资料下载

参数资料

| 型号: | ADS8364Y/250G4 |

| 厂商: | Texas Instruments |

| 文件页数: | 23/26页 |

| 文件大小: | 0K |

| 描述: | IC ADC LP 16BIT 250KSPS 64-TQFP |

| 产品培训模块: | Data Converter Basics |

| 标准包装: | 250 |

| 位数: | 16 |

| 采样率(每秒): | 250k |

| 数据接口: | 并联 |

| 转换器数目: | 6 |

| 功率耗散(最大): | 471.5mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-TQFP |

| 供应商设备封装: | 64-TQFP(10x10) |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 12 个单端,双极;6 个差分,双极 |

| 配用: | 296-30708-ND - EVAL MODULE FOR ADS8364 ADS8364EVM-ND - EVALUATION MODULE FOR BQ2018 |

ADS8364

6

SBAS219C

www.ti.com

SPEC

DESCRIPTION

MIN

TYP(1)

MAX

UNITS

tCONV

Conversion Time

3.2

s

tACQ

Acquistion Time

0.8

s

tC1

Cycle Time of CLK

200

ns

tW1

Pulse Width CLK HIGH Time or LOW Time.

60

ns

tD1(5)

Delay Time of Rising Edge of Clock After Falling Edge of HOLD (A,B,C)

10

ns

tW2

Pulse Width of HOLDX HIGH Time to be Recognized again

BVDD = 5V

15

ns

BVDD = 3V

30

ns

tW3

Pulse Width of HOLDX LOW Time

BVDD = 5V

20

ns

BVDD = 3V

30

ns

tW4

Pulse Width of RESET

BVDD = 5V

20

ns

BVDD = 3V

40

ns

tW5

Pulse Width of RD HIGH Time

BVDD = 5V

30

ns

BVDD = 3V

40

ns

tD2

Delay Time of First Hold After RESET

BVDD = 5V

20

ns

BVDD = 3V

40

ns

tD4

Delay Time of Falling Edge of RD After Falling Edge of CS

0

ns

tD5

Delay Time of Rising Edge of CS After Rising Edge of RD

0

ns

tW6

Pulse Width of RD and CS Both LOW Time

BVDD = 5V

50

ns

BVDD = 3V

70

ns

tW7

Pulse Width of RD HIGH Time

BVDD = 5V

20

ns

BVDD = 3V

40

ns

tD6

Delay Time of Data Valid After Falling Edge RD

BVDD = 5V

40

ns

BVDD = 3V

60

ns

tD7

Delay Time of Data Hold From Rising Edge of RD

BVDD = 5V

5

ns

BVDD = 3V

10

ns

tD8

Delay Time of RD HIGH After CS LOW

BVDD = 5V

50

ns

BVDD = 3V

60

ns

tD9

Delay Time of RD Low After Address Setup

BVDD = 5V

10

ns

BVDD = 3V

20

ns

NOTES: (1) Assured by design. (2) All input signals are specified with tr = tf = 5ns (10% to 90% of BVDD) and timed from a voltage level of (VIL + VIH)/2.

(3) See timing diagram above. (4) BYTE is asynchronous; when BYTE is 0, bits 15 through 0 appear at DB15-DB0. When BYTE is 1, bits 15 through 8

appear on DB7-DB0. RD may remain LOW between changes in BYTE. (5) Only important when synchronization to clock is important.

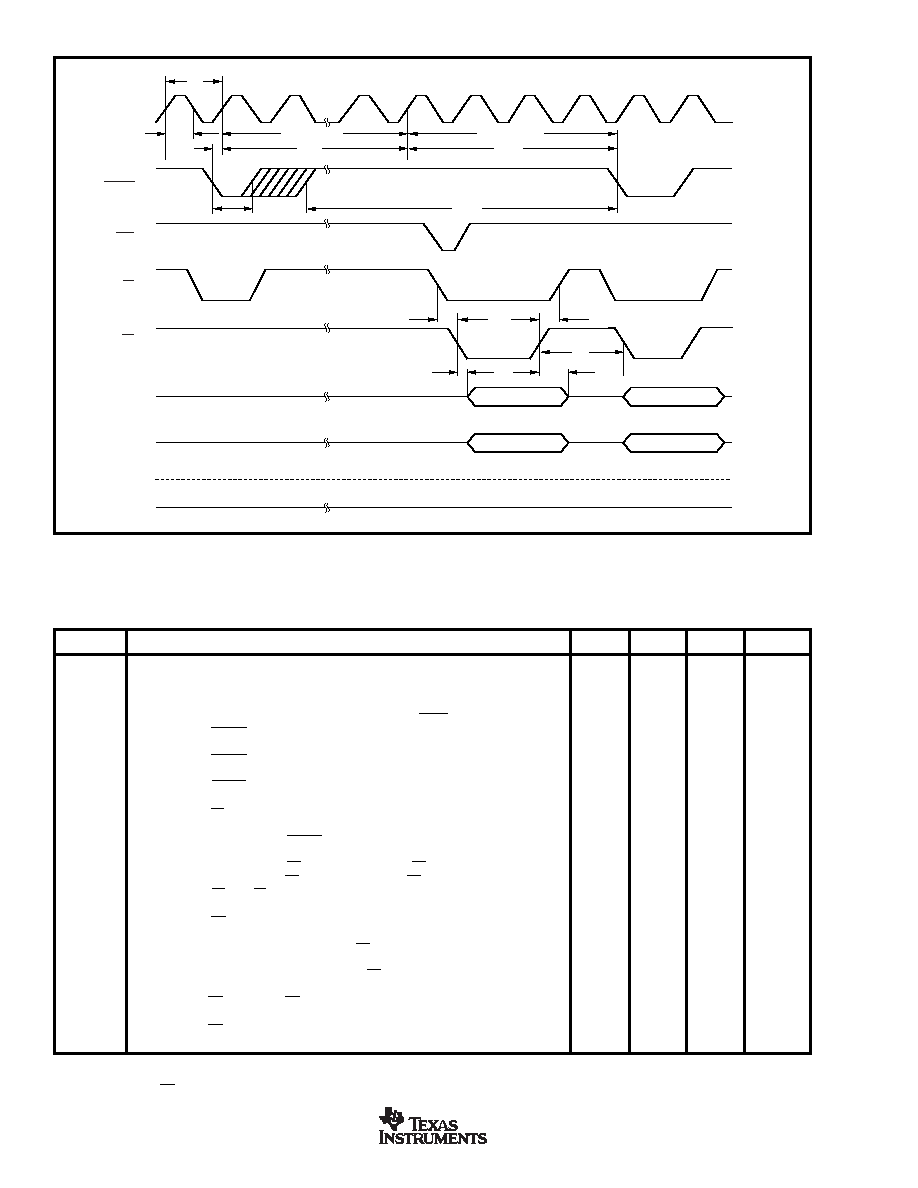

TIMING CHARACTERISTICS TABLE

Timing Characteristics over recommended operating free-air temperature range T

MIN to TMAX, AVDD = DVDD = 5V, REFIN = REFOUT internal reference +2.5V,

f

CLK = 5MHz, fSAMPLE = 250kSPS, BVDD = 2.7 ÷ 5V (unless otherwise noted).

TIMING CHARACTERISTICS

t

W6

t

D6

t

D4

t

D5

t

D7

t

W5

t

W1

t

D1

t

C1

t

W3

CONVERSION

t

CONV

ACQUISITION

t

ACQ

t

W2

Bits 15-8

Bits 7-0

Bits 15-8

Bits 7-0

CLK

HOLDX

EOC

CS

RD

D15-D8

D7-D0

BYTE

1

2

16

17

18

19

20

1

2

相关PDF资料 |

PDF描述 |

|---|---|

| ADS8412IPFBRG4 | IC ADC 16BIT 2MSPS 48-TQFP |

| ADV7180WBCPZ | IC VIDEO DECODER SDTV 40LFCSP |

| ADV7186BBCZ | IC VIDEO DECODER 196CSPBGA |

| ADV7441ABSTZ-5P | IC DECODER DIGITIZER 144LQFP |

| ADV7513BSWZ | IC TX HDMI 165MHZ 64LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADS8365 | 制造商:BB 制造商全称:BB 功能描述:16-Bit, 250kSPS, 6-Channel, Simultaneous Sampling SAR ANALOG-TO-DIGITAL CONVERTERS |

| ADS8365IPAG | 功能描述:模数转换器 - ADC 16B 250kSPS 6Ch Simu Sampling SAR ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| ADS8365IPAGG4 | 功能描述:模数转换器 - ADC 16B 250kSPS 6Ch Simu Sampling SAR ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| ADS8365IPAGG-4 | 制造商:Texas Instruments 功能描述:IC, SM 16-BIT ADC 6CH SAR |

| ADS8365IPAGR | 功能描述:模数转换器 - ADC 16 B 250k SPS 6 Ch Smltns Smplg SARADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。