- 您现在的位置:买卖IC网 > PDF目录19400 > ADSP-21479KBCZ-1A (Analog Devices Inc)IC DSP SHARK 200MHZ 196CSPBGA PDF资料下载

参数资料

| 型号: | ADSP-21479KBCZ-1A |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/76页 |

| 文件大小: | 0K |

| 描述: | IC DSP SHARK 200MHZ 196CSPBGA |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | DAI,DPI,EBI/EMI,I²C,SPI,SPORT,UART/USART |

| 时钟速率: | 200MHz |

| 非易失内存: | ROM(4Mb) |

| 芯片上RAM: | 5Mb |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 196-LFBGA,CSPBGA |

| 供应商设备封装: | 196-CSPBGA(12x12) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

Rev. C

|

Page 19 of 76

|

July 2013

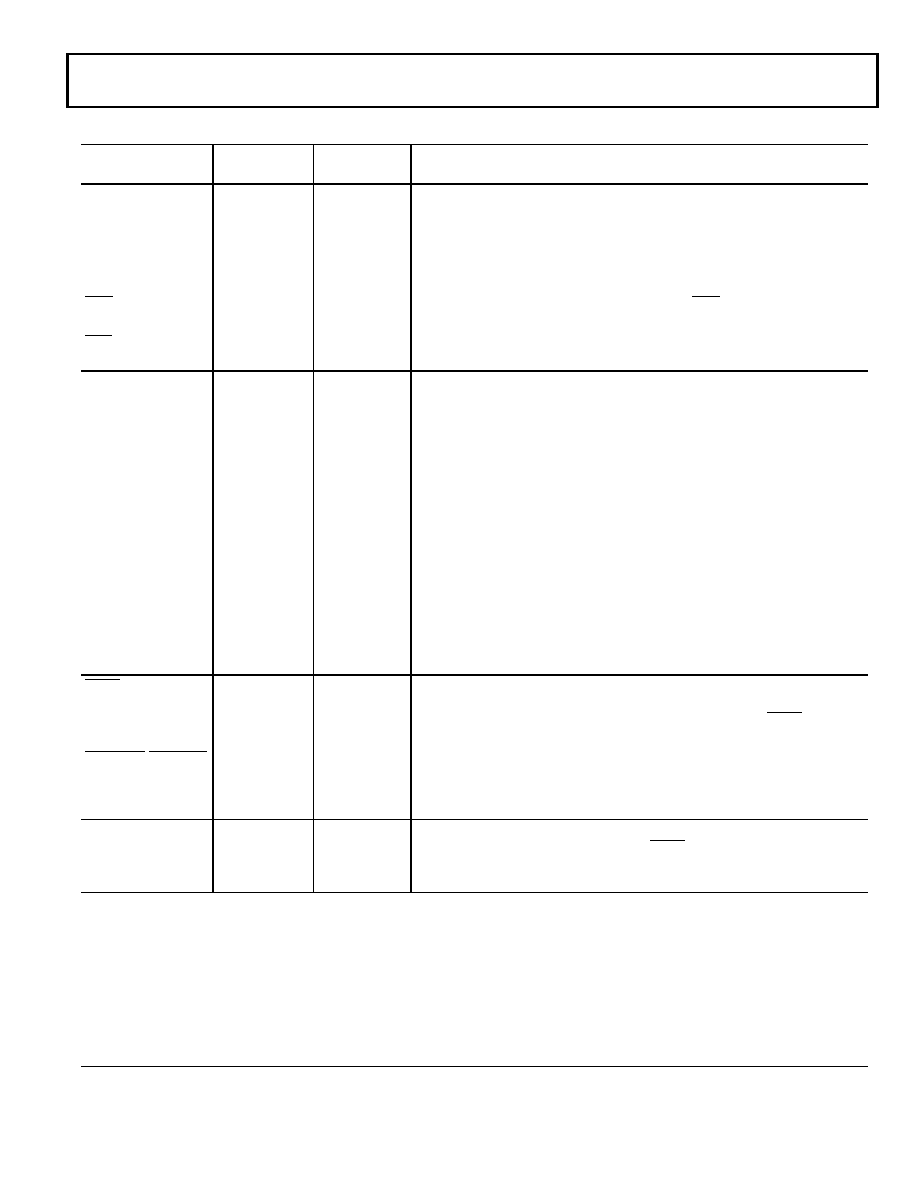

TDI

I (ipu)

Test Data Input (JTAG). Provides serial data for the boundary scan logic.

TDO

O/T

High-Z

Test Data Output (JTAG). Serial scan output of the boundary scan path.

TMS

I (ipu)

Test Mode Select (JTAG). Used to control the test state machine.

TCK

I

Test Clock (JTAG). Provides a clock for JTAG boundary scan. TCK must be asserted

(pulsed low) after power-up or held low for proper operation of the device.

TRST

I (ipu)

Test Reset (JTAG). Resets the test state machine. TRST must be asserted (pulsed

low) after power-up or held low for proper operation of the processor.

EMU

O (O/D, ipu)

High-Z

Emulation Status. Must be connected to the Analog Devices DSP Tools product

line of JTAG emulators target board connector only.

CLK_CFG1–0

I

Core to CLKIN Ratio Control. These pins set the startup clock frequency.

Note that the operating frequency can be changed by programming the PLL

multiplier and divider in the PMCTL register at any time after the core comes out

of reset. The allowed values are:

00 = 8:1

01 = 32:1

10 = 16:1

11 = reserved

CLKIN

I

Local Clock In. Used in conjunction with XTAL. CLKIN is the clock input. It

configures the processors to use either its internal clock generator or an external

clock source. Connecting the necessary components to CLKIN and XTAL enables

the internal clock generator. Connecting the external clock to CLKIN while leaving

XTAL unconnected configures the processors to use the external clock source

such as an external clock oscillator. CLKIN may not be halted, changed, or

operated below the specified frequency.

XTAL

O

Crystal Oscillator Terminal. Used in conjunction with CLKIN to drive an external

crystal.

RESET

I

Processor Reset. Resets the processor to a known state. Upon deassertion, there

is a 4096 CLKIN cycle latency for the PLL to lock. After this time, the core begins

program execution from the hardware reset vector address. The RESET input must

be asserted (low) at power-up.

RESETOUT/RUNRSTIN I/O (ipu)

Reset Out/Running Reset In. The default setting on this pin is reset out. This pin

also has a second function as RUNRSTIN which is enabled by setting bit 0 of the

RUNRSTCTL register. For more information, see the ADSP-214xx SHARC Processor

Hardware Reference.

BOOT_CFG2–0

I

Boot Configuration Select. These pins select the boot mode for the processor.

The BOOT_CFG pins must be valid before RESET (hardware and software) is de-

asserted.

The BOOT_CFG2 pin is only available on the 196-lead package.

Table 11. Pin Descriptions (Continued)

Name

Type

State During/

After Reset

Description

The following symbols appear in the Type column of Table 11: A = asynchronous, I =input, O = output, S = synchronous, A/D = active drive,

O/D = open drain, and T = three-state, ipd = internal pull-down resistor, ipu = internal pull-up resistor.

The internal pull-up (ipu) and internal pull-down (ipd) resistors are designed to hold the internal path from the pins at the expected logic

levels. To pull-up or pull-down the external pads to the expected logic levels, use external resistors. Internal pull-up/pull-down resistors

cannot be enabled/disabled and the value of these resistors cannot be programmed. The range of an ipu resistor can be 26 kΩ to 63 kΩ. The

range of an ipd resistor can be 31 kΩ to 85 kΩ. The three-state voltage of ipu pads will not reach to full the VDD_EXT level; at typical conditions

the voltage is in the range of 2.3 V to 2.7 V.

In this table, all pins are LVTTL compliant with the exception of the thermal diode, shift register, and real-time clock (RTC) pins.

Not all pins are available in the 88-lead LFCSP_VQ and 100-lead LQFP package. For more information, see Table 2 on Page 3 and Table 62 on

Page 70.

相关PDF资料 |

PDF描述 |

|---|---|

| MLP2520S2R2S | INDUCTOR MULTILAYER 2.2UH 1008 |

| MAX6518UKP035+T | IC TEMP SENSOR SW SOT23-5 |

| VI-23D-CY-F1 | CONVERTER MOD DC/DC 85V 50W |

| GEC12DRXH-S734 | CONN EDGECARD 24POS DIP .100 SLD |

| VI-B6J-EU-B1 | CONVERTER MOD DC/DC 36V 200W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21479KBCZ-2A | 功能描述:IC DSP SHARC 266MHZ LP 196CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21479KBCZ-3A | 功能描述:IC DSP SHARK 300MHZ 196CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21479KBCZ-3AX | 制造商:Analog Devices 功能描述:- Trays |

| ADSP-21479KBCZ-ENG | 制造商:Analog Devices 功能描述:SHARC PROCESSOR - Trays |

| ADSP-21479KCPZ-1A | 功能描述:IC DSP SHARK 200MHZ 88LFCSP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。