- 您现在的位置:买卖IC网 > PDF目录19505 > ADSP-BF536BBCZ-4A (Analog Devices Inc)IC DSP CTLR 16BIT 182CSPBGA PDF资料下载

参数资料

| 型号: | ADSP-BF536BBCZ-4A |

| 厂商: | Analog Devices Inc |

| 文件页数: | 7/68页 |

| 文件大小: | 0K |

| 描述: | IC DSP CTLR 16BIT 182CSPBGA |

| 产品培训模块: | Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | CAN,SPI,SSP,TWI,UART |

| 时钟速率: | 400MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 100kB |

| 电压 - 输入/输出: | 2.50V,3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 182-LFBGA,CSPBGA |

| 供应商设备封装: | 182-CSPBGA(12x12) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

Rev. J

|

Page 15 of 68

|

February 2014

hibernate state, VDDEXT can still be applied, eliminating the need

for external buffers. The voltage regulator can be activated from

this power-down state by asserting the RESET pin, which then

initiates a boot sequence. The regulator can also be disabled and

bypassed at the user’s discretion. For additional information on

voltage regulation, see Switching Regulator Design Consider-

ations for the ADSP-BF533 Blackfin Processors (EE-228).

CLOCK SIGNALS

The ADSP-BF534/ADSP-BF536/ADSP-BF537 processors can

be clocked by an external crystal, a sine wave input, or a buff-

ered, shaped clock derived from an external clock oscillator.

If an external clock is used, it should be a TTL compatible signal

and must not be halted, changed, or operated below the speci-

fied frequency during normal operation. This signal is

connected to the processor’s CLKIN pin. When an external

clock is used, the XTAL pin must be left unconnected.

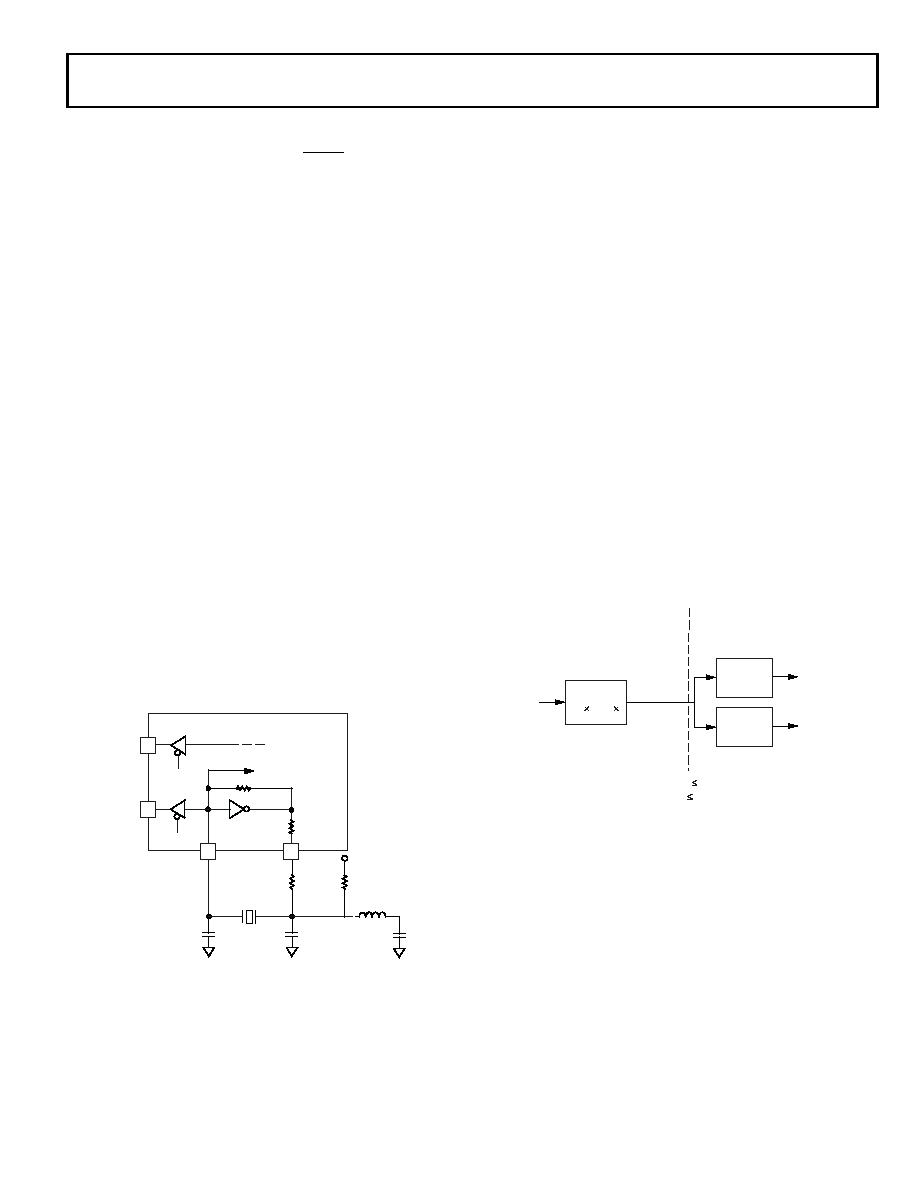

Alternatively, because the processors include an on-chip oscilla-

tor circuit, an external crystal can be used. For fundamental

frequency operation, use the circuit shown in Figure 6. A

parallel-resonant, fundamental frequency, microprocessor-

grade crystal is connected across the CLKIN and XTAL pins.

The on-chip resistance between CLKIN and the XTAL pin is in

the 500 k range. Further parallel resistors are typically not rec-

ommended. The two capacitors and the series resistor shown in

Figure 6 fine-tune phase and amplitude of the sine frequency.

The capacitor and resistor values shown in Figure 6 are typical

values only. The capacitor values are dependent upon the crystal

manufacturers’ load capacitance recommendations and the PCB

physical layout. The resistor value depends on the drive level

specified by the crystal manufacturer. The user should verify the

customized values based on careful investigations of multiple

devices over temperature range.

A third-overtone crystal can be used for frequencies above

25 MHz. The circuit is then modified to ensure crystal operation

only at the third overtone, by adding a tuned inductor circuit as

shown in Figure 6. A design procedure for third-overtone oper-

ation is discussed in detail in the application note Using Third

Overtone Crystals with the ADSP-218x DSP (EE-168).

The CLKBUF pin is an output pin, and is a buffer version of the

input clock. This pin is particularly useful in Ethernet applica-

tions to limit the number of required clock sources in the

system. In this type of application, a single 25 MHz or 50 MHz

crystal can be applied directly to the processors. The 25 MHz or

50 MHz output of CLKBUF can then be connected to an exter-

nal Ethernet MII or RMII PHY device.

Because of the default 10× PLL multiplier, providing a 50 MHz

CLKIN exceeds the recommended operating conditions of the

lower speed grades. Because of this restriction, an RMII PHY

requiring a 50 MHz clock input cannot be clocked directly from

the CLKBUF pin for the lower speed grades. In this case, either

provide a separate 50 MHz clock source, or use an RMII PHY

with 25 MHz clock input options. The CLKBUF output is active

by default and can be disabled using the VR_CTL register for

power savings.

The Blackfin core runs at a different clock rate than the on-chip

peripherals. As shown in Figure 7, the core clock (CCLK) and

system peripheral clock (SCLK) are derived from the input

clock (CLKIN) signal. An on-chip PLL is capable of multiplying

the CLKIN signal by a programmable 0.5× to 64× multiplication

factor (bounded by specified minimum and maximum VCO

frequencies). The default multiplier is 10×, but it can be modi-

fied by a software instruction sequence in the PLL_CTL register.

On-the-fly CCLK and SCLK frequency changes can be effected

by simply writing to the PLL_DIV register. Whereas the maxi-

mum allowed CCLK and SCLK rates depend on the applied

voltages VDDINT and VDDEXT, the VCO is always permitted to run

up to the frequency specified by the part’s speed grade. The

CLKOUT pin reflects the SCLK frequency to the off-chip world.

It belongs to the SDRAM interface, but it functions as a refer-

ence signal in other timing specifications as well. While active

by default, it can be disabled using the EBIU_SDGCTL and

EBIU_AMGCTL registers.

All on-chip peripherals are clocked by the system clock (SCLK).

The system clock frequency is programmable by means of the

SSEL3–0 bits of the PLL_DIV register. The values programmed

into the SSEL fields define a divide ratio between the PLL output

Figure 6. External Crystal Connections

CLKIN

CLKOUT

XTAL

EN

CLKBUF

TO PLL CIRCUITRY

FOR OVERTONE

OPERATION ONLY:

NOTE: VALUES MARKED WITH * MUST BE CUSTOMIZED, DEPENDING

ON THE CRYSTAL AND LAYOUT. PLEASE ANALYZE CAREFULLY.

18 pF *

EN

18 pF *

330

*

BLACKFIN

350

1M

V

DDEXT

Figure 7. Frequency Modification Methods

PLL

0.5 to 64

÷1 to 15

÷1,2, 4, 8

VCO

CLKIN

“FINE” ADJUSTMENT

REQUIRES PLL SEQUENCING

“COARSE” ADJUSTMENT

ON-THE-FLY

CCLK

SCLK

CCLK

SCLK

133 MHz

相关PDF资料 |

PDF描述 |

|---|---|

| XC9536XL-5PC44C | IC CPLD 36 MCELL 3.3V 44-PLCC |

| ABM36DSXH | CONN EDGECARD 72POS DIP .156 SLD |

| RCM10DTKD-S288 | CONN EDGECARD 20POS .156 EXTEND |

| XC9536XL-10PC44I | IC CPLD 36 MCELL I-TEMP 44-PLCC |

| V300A24E400BF | CONVERTER MOD DC/DC 24V 400W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF536BBCZ-4B | 功能描述:IC DSP CTLR 16BIT 208CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-BF536BBCZ4BRL | 功能描述:IC DSP CTLR 16BIT 208CSBGA 制造商:analog devices inc. 系列:Blackfin? 包装:带卷(TR) 零件状态:有效 类型:定点 接口:CAN,SPI,SSP,TWI,UART 时钟速率:400MHz 非易失性存储器:外部 片载 RAM:100kB 电压 - I/O:2.50V,3.30V 电压 - 内核:1.20V 工作温度:-40°C ~ 85°C(TA) 安装类型:表面贴装 封装/外壳:208-FBGA,CSPBGA 供应商器件封装:208-CSPBGA(17x17) 标准包装:1,000 |

| ADSP-BF536SBBC2Z300 | 制造商:Analog Devices 功能描述: |

| ADSP-BF536SBBC2Z400 | 制造商:Analog Devices 功能描述: |

| ADSP-BF537BBC-5A | 功能描述:IC DSP CTLR 16BIT 182CSPBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。