- 您现在的位置:买卖IC网 > PDF目录19387 > ADSP-BF537BBCZ-5AV (Analog Devices Inc)IC DSP CTLR 16BIT 182CSPBGA PDF资料下载

参数资料

| 型号: | ADSP-BF537BBCZ-5AV |

| 厂商: | Analog Devices Inc |

| 文件页数: | 43/68页 |

| 文件大小: | 0K |

| 描述: | IC DSP CTLR 16BIT 182CSPBGA |

| 产品培训模块: | Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | CAN,SPI,SSP,TWI,UART |

| 时钟速率: | 533MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 132kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.25V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 182-LFBGA,CSPBGA |

| 供应商设备封装: | 182-CSPBGA(12x12) |

| 包装: | 托盘 |

| 配用: | ADZS-BF537-ASKIT-ND - BOARD EVAL SKIT ADSP-BF537 ADZS-BFAUDIO-EZEXT-ND - BOARD EVAL AUDIO BLACKFIN ADZS-BF537-EZLITE-ND - BOARD EVAL ADSP-BF537 ADZS-BFAV-EZEXT-ND - BOARD DAUGHT ADSP-BF533,37,61KIT ADZS-BF537-STAMP-ND - SYSTEM DEV FOR ADSP-BF537 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页当前第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

Rev. J

|

Page 48 of 68

|

February 2014

Table 44. 10/100 Ethernet MAC Controller Timing: MII/RMII Asynchronous Signal

Parameter

1, 2

Min

Max

Unit

tECOLH

COL Pulse Width High

tETxCLK × 1.5

tERxCLK × 1.5

ns

tECOLL

COL Pulse Width Low

tETxCLK × 1.5

tERxCLK × 1.5

ns

tECRSH

CRS Pulse Width High

tETxCLK × 1.5

ns

tECRSL

CRS Pulse Width Low

tETxCLK × 1.5

ns

1 MII/RMII asynchronous signals are COL, CRS. These signals are applicable in both MII and RMII modes. The asynchronous COL input is synchronized separately to both

the ETxCLK and the ERxCLK, and must have a minimum pulse width high or low at least 1.5 times the period of the slower of the two clocks.

2 The asynchronous CRS input is synchronized to the ETxCLK, and must have a minimum pulse width high or low at least 1.5 times the period of ETxCLK.

Table 45. 10/100 Ethernet MAC Controller Timing: MII Station Management

Parameter

1

Min

Max

Unit

tMDIOS

MDIO Input Valid to MDC Rising Edge (Setup)

10

ns

tMDCIH

MDC Rising Edge to MDIO Input Invalid (Hold)

10

ns

tMDCOV

MDC Falling Edge to MDIO Output Valid

25

ns

tMDCOH

MDC Falling Edge to MDIO Output Invalid (Hold)

–1

ns

1 MDC/MDIO is a 2-wire serial bidirectional port for controlling one or more external PHYs. MDC is an output clock whose minimum period is programmable as a multiple

of the system clock SCLK. MDIO is a bidirectional data line.

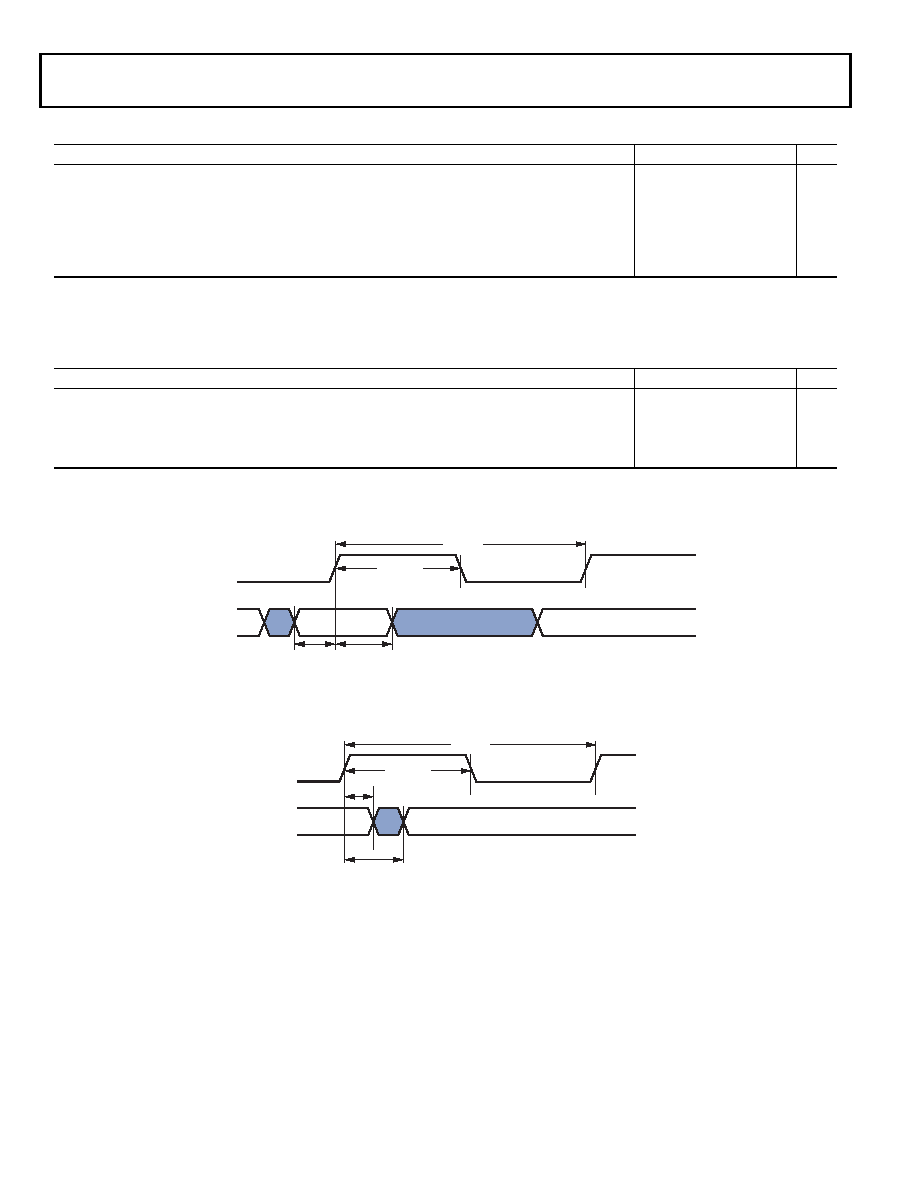

Figure 30. 10/100 Ethernet MAC Controller Timing: MII Receive Signal

Figure 31. 10/100 Ethernet MAC Controller Timing: MII Transmit Signal

tERXCLKIS tERXCLKIH

ERxD3–0

ERxDV

ERxER

ERx_CLK

tERXCLKW

tERXCLK

tETXCLKOH

ETxD3–0

ETxEN

MIITxCLK

tETXCLK

tETXCLKOV

tETXCLKW

相关PDF资料 |

PDF描述 |

|---|---|

| TPSD157M006Y0125 | CAP TANT 150UF 6.3V 20% 2917 |

| RW2-243.3D/H3/B | CONV DC/DC 2W 18-36VIN +/-3.3V |

| AMC26DREN | CONN EDGECARD 52POS .100 EYELET |

| ACC40DREN | CONN EDGECARD 80POS .100 EYELET |

| RCC05DRYH | CONN EDGECARD 10POS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF537BBCZ-5AV | 制造商:Analog Devices 功能描述:Digital Signal Processor IC |

| ADSP-BF537BBCZ5AVX | 制造商:Analog Devices 功能描述:- Trays |

| ADSP-BF537BBCZ-5AVX | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| ADSP-BF537BBCZ-5AX | 制造商:Analog Devices 功能描述:182-MBGA PB-FREE - Trays |

| ADSP-BF537BBCZ-5B | 功能描述:IC DSP CTLR 16BIT 208CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。