- 您现在的位置:买卖IC网 > PDF目录19504 > ADSP-BF537KBCZ-6AV (Analog Devices Inc)IC DSP CTLR 16BIT 182CSPBGA PDF资料下载

参数资料

| 型号: | ADSP-BF537KBCZ-6AV |

| 厂商: | Analog Devices Inc |

| 文件页数: | 42/68页 |

| 文件大小: | 0K |

| 描述: | IC DSP CTLR 16BIT 182CSPBGA |

| 产品培训模块: | Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | 定点 |

| 接口: | CAN,SPI,SSP,TWI,UART |

| 时钟速率: | 600MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 132kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.30V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 182-LFBGA,CSPBGA |

| 供应商设备封装: | 182-CSPBGA(12x12) |

| 包装: | 托盘 |

| 配用: | ADZS-BF537-ASKIT-ND - BOARD EVAL SKIT ADSP-BF537 ADZS-BFAUDIO-EZEXT-ND - BOARD EVAL AUDIO BLACKFIN ADZS-BF537-EZLITE-ND - BOARD EVAL ADSP-BF537 ADZS-BFAV-EZEXT-ND - BOARD DAUGHT ADSP-BF533,37,61KIT ADZS-BF537-STAMP-ND - SYSTEM DEV FOR ADSP-BF537 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页当前第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

Rev. J

|

Page 47 of 68

|

February 2014

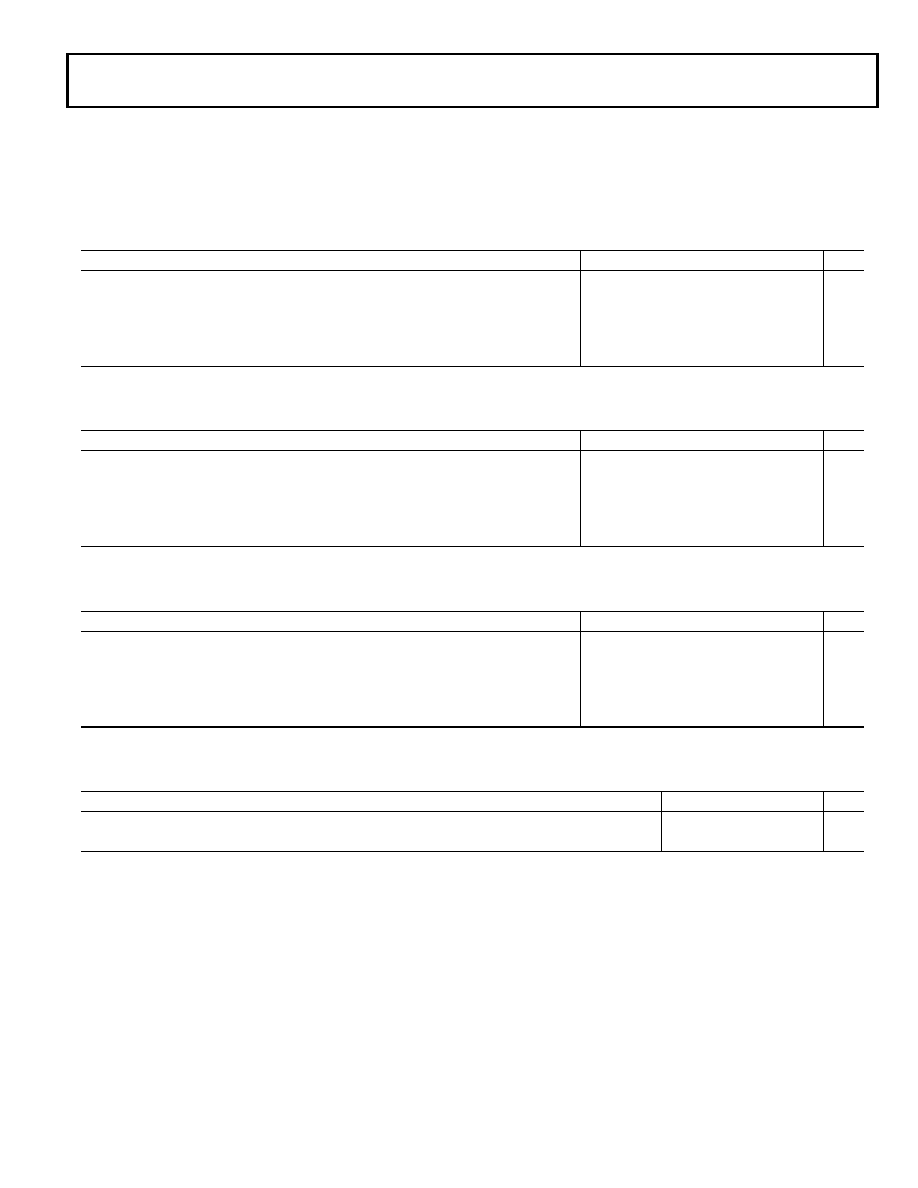

10/100 Ethernet MAC Controller Timing

describe the 10/100 Ethernet MAC controller operations. This

feature is only available on the ADSP-BF536 and ADSP-BF537

processors.

Table 40. 10/100 Ethernet MAC Controller Timing: MII Receive Signal

Parameter1

Min

Max

Unit

fERXCLK

ERxCLK Frequency (fSCLK = SCLK Frequency)

None

25 + 1%

fSCLK + 1%

MHz

tERXCLKW

ERxCLK Width (tERxCLK = ERxCLK Period)

tERxCLK × 35%

tERxCLK × 65%

ns

tERXCLKIS

Rx Input Valid to ERxCLK Rising Edge (Data In Setup)

7.5

ns

tERXCLKIH

ERxCLK Rising Edge to Rx Input Invalid (Data In Hold)

7.5

ns

1 MII inputs synchronous to ERxCLK are ERxD3–0, ERxDV, and ERxER.

Table 41. 10/100 Ethernet MAC Controller Timing: MII Transmit Signal

Parameter1

Min

Max

Unit

fETXCLK

ETxCLK Frequency (fSCLK = SCLK Frequency)

None

25 + 1%

fSCLK + 1%

MHz

tETXCLKW

ETxCLK Width (tETXCLK = ETxCLK Period)

tETxCLK × 35%

tETxCLK × 65%

ns

tETXCLKOV

ETxCLK Rising Edge to Tx Output Valid (Data Out Valid)

20

ns

tETXCLKOH

ETxCLK Rising Edge to Tx Output Invalid (Data Out Hold)

0

ns

1 MII outputs synchronous to ETxCLK are ETxD3–0.

Table 42. 10/100 Ethernet MAC Controller Timing: RMII Receive Signal

Parameter

1

Min

Max

Unit

fREFCLK

REF_CLK Frequency (fSCLK = SCLK Frequency)

None

50 + 1%

2 × fSCLK + 1%

MHz

tREFCLKW

REF_CLK Width (tREFCLK = REFCLK Period)

tREFCLK × 35%

tREFCLK × 65%

ns

tREFCLKIS

Rx Input Valid to RMII REF_CLK Rising Edge (Data In Setup)

4

ns

tREFCLKIH

RMII REF_CLK Rising Edge to Rx Input Invalid (Data In Hold)

2

ns

1 RMII inputs synchronous to RMII REF_CLK are ERxD1–0, RMII CRS_DV, and ERxER.

Table 43. 10/100 Ethernet MAC Controller Timing: RMII Transmit Signal

Parameter

1

Min

Max

Unit

tREFCLKOV

RMII REF_CLK Rising Edge to Tx Output Valid (Data Out Valid)

7.5

ns

tREFCLKOH

RMII REF_CLK Rising Edge to Tx Output Invalid (Data Out Hold)

2

ns

1 RMII outputs synchronous to RMII REF_CLK are ETxD1–0.

相关PDF资料 |

PDF描述 |

|---|---|

| V300A2E160BL | CONVERTER MOD DC/DC 2V 160W |

| ADSP-2191MKSTZ-160 | IC DSP CONTROLLER 16BIT 144LQFP |

| MLP2012S2R2T | INDUCTOR MULTILAYER 2.2UH 0805 |

| 10090098-S254VLF | DSUB STR 25POS SOCKET |

| ADSP-BF527KBCZ-6A | IC DSP 16BIT 600MHZ 208CSPBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-BF537KBCZ6AVX | 制造商:Analog Devices 功能描述:- Trays |

| ADSP-BF537KBCZ-6B | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 600MHz 600MIPS 208-Pin CSP-BGA 制造商:Rochester Electronics LLC 功能描述: |

| ADSP-BF537KBCZ-6BV | 功能描述:IC DSP CTLR 16BIT 208CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:Blackfin® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-BF537KBCZ6BVX | 制造商:Analog Devices 功能描述:- Trays |

| ADSP-BF537KBCZ-6BVX | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。