- 您现在的位置:买卖IC网 > PDF目录166212 > AM29DS323DT110EI (ADVANCED MICRO DEVICES INC) Hex Inverters 14-TSSOP -40 to 85 PDF资料下载

参数资料

| 型号: | AM29DS323DT110EI |

| 厂商: | ADVANCED MICRO DEVICES INC |

| 元件分类: | PROM |

| 英文描述: | Hex Inverters 14-TSSOP -40 to 85 |

| 中文描述: | 2M X 16 FLASH 1.8V PROM, 110 ns, PDSO48 |

| 封装: | MO-142DD, TSOP-48 |

| 文件页数: | 3/53页 |

| 文件大小: | 985K |

| 代理商: | AM29DS323DT110EI |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页

Am29DS323D

11

P R E L I M I NARY

30 ns. The automatic sleep mode is independent of

the CE#, WE#, and OE# control signals. Standard ad-

dres s ac c e s s t i mings pro v ide new dat a when

addresses are changed. While in sleep mode, output

data is latched and always available to the system.

I

CC4 in the DC Characteristics table represents the

automatic sleep mode current specification.

RESET#: Hardware Reset Pin

The RESET# pin provides a hardware method of re-

setting the device to reading array data. When the

RESET# pin is driven low for at least a period of t

RP,

the device immediately terminates any operation in

progress, tristates all output pins, and ignores all

read/write commands for the duration of the RESET#

pulse. The device also resets the internal state ma-

chine to reading array data. The operation that was

interrupted should be reinitiated once the device is

ready to accept another command sequence, to en-

sure data integrity.

Current is reduced for the duration of the RESET#

pulse. When RESET# is held at V

SS±0.3 V, the device

draws CMOS standby current (I

CC4). If RESET# is held

at V

IL but not within VSS±0.3 V, the standby current will

be greater.

The RESET# pin may be tied to the system reset cir-

cuitry. A system reset would thus also reset the Flash

memory, enabling the system to read the boot-up firm-

ware from the Flash memory.

If RESET# is asserted during a program or erase op-

eration, the RY/BY# pin remains a “0” (busy) until the

internal reset operation is complete, which requires a

time of t

READY (during Embedded Algorithms). The sys-

tem can thus monitor RY/BY# to determine whether

the reset operation is complete. If RESET# is asserted

when a program or erase operation is not executing

(RY/BY# pin is “1”), the reset operation is completed

within a time of t

READY (not during Embedded Algo-

rithms). The system can read data t

RH after th e

RESET# pin returns to V

IH.

Refer to the AC Characteristics tables for RESET# pa-

rameters and to Figure 14 for the timing diagram.

Output Disable Mode

When the OE# input is at V

IH, output from the device is

disabled. The output pins are placed in the high

impedance state.

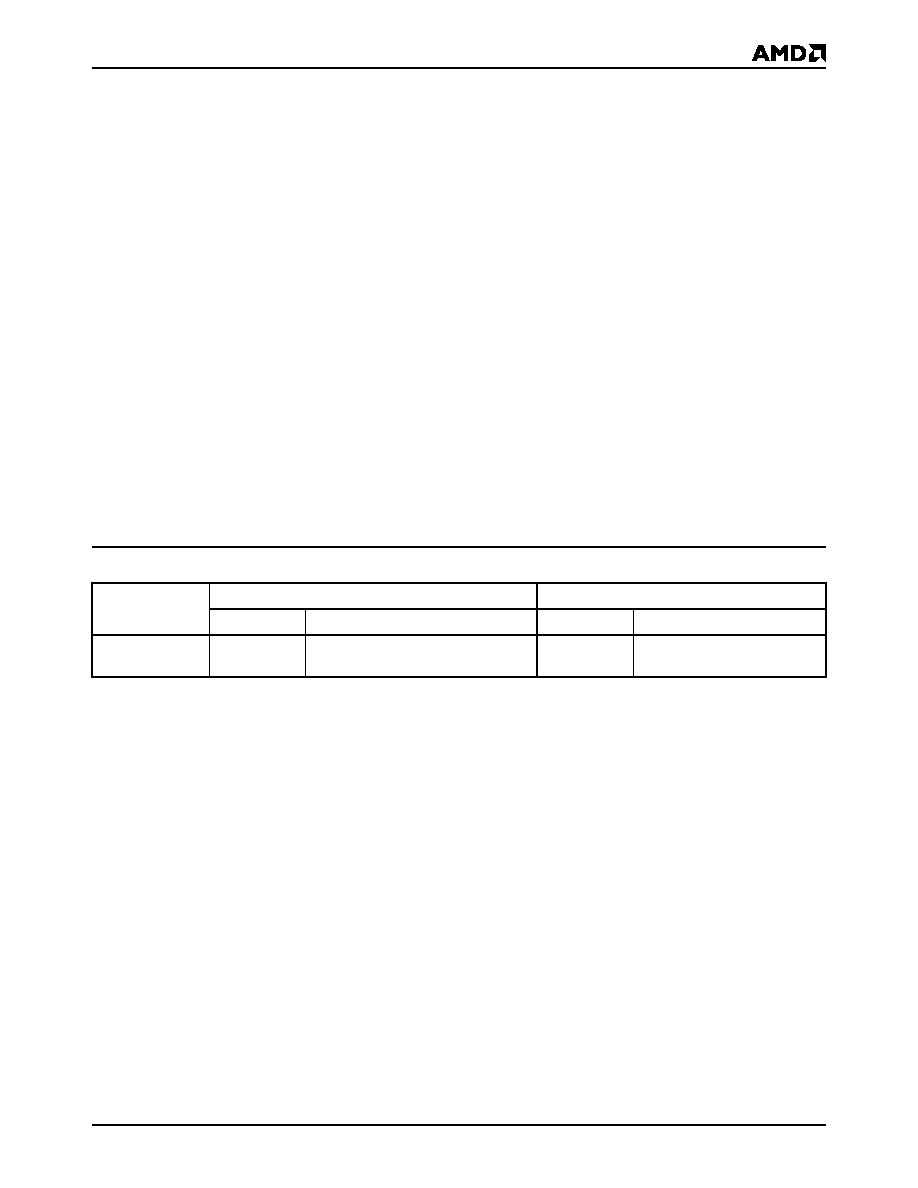

Table 2.

Am29DS323D Device Bank Divisions

Device

Part Number

Bank 1

Bank 2

Megabits

Sector Sizes

Megabits

Sector Sizes

Am29DS323D

8 Mbit

Eight 8 Kbyte/4 Kword,

fifteen 64 Kbyte/32 Kword

24 Mbit

Forty-eight

64 Kbyte/32 Kword

相关PDF资料 |

PDF描述 |

|---|---|

| AM29DS323DT120EI | Hex Inverters 14-TSSOP -40 to 85 |

| AM29DS323DT120WMI | Hex Inverters 14-TSSOP -40 to 85 |

| AM29DS323D | Hex Inverters 14-TSSOP -40 to 85 |

| AM29DS323DT110 | Hex Inverters 14-TSSOP -40 to 85 |

| AM29DS323DT120 | 32 Megabit (4 M x 8-Bit/2 M x 16-Bit) CMOS 1.8 Volt-only, Simultaneous Operation Flash Memory |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AM29DS323DT-110WMI | 制造商:Spansion 功能描述:NOR Flash Parallel 32Mbit 4M/2M x 8bit/16bit 110ns 48-Pin FBGA |

| AM29DS323DT11WMINS | 制造商:Advanced Micro Devices 功能描述: |

| AM29F002B-70JC | 制造商:Advanced Micro Devices 功能描述:NOR Flash, 256K x 8, 32 Pin, Plastic, PLCC |

| AM29F002BB-120EC | 制造商:Spansion 功能描述:2M (256KX8) 5V, BOOT BLOCK, BOT, TSOP32, COM - Trays |

| AM29F002BB-120JCT | 制造商:Spansion 功能描述:2M (256KX8) 5V, BOOT BLOCK, BOT, PLCC32, COM, T&R - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。