- 您现在的位置:买卖IC网 > PDF目录381488 > AT6005LV-4JC (ATMEL CORP) Coprocessor Field Programmable Gate Arrays PDF资料下载

参数资料

| 型号: | AT6005LV-4JC |

| 厂商: | ATMEL CORP |

| 元件分类: | FPGA |

| 英文描述: | Coprocessor Field Programmable Gate Arrays |

| 中文描述: | FPGA, 3136 CLBS, 15000 GATES, PQCC84 |

| 封装: | PLASTIC, MS-018AF, LCC-84 |

| 文件页数: | 7/28页 |

| 文件大小: | 835K |

| 代理商: | AT6005LV-4JC |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

AT6000(LV) Series

7

Clock Distribution

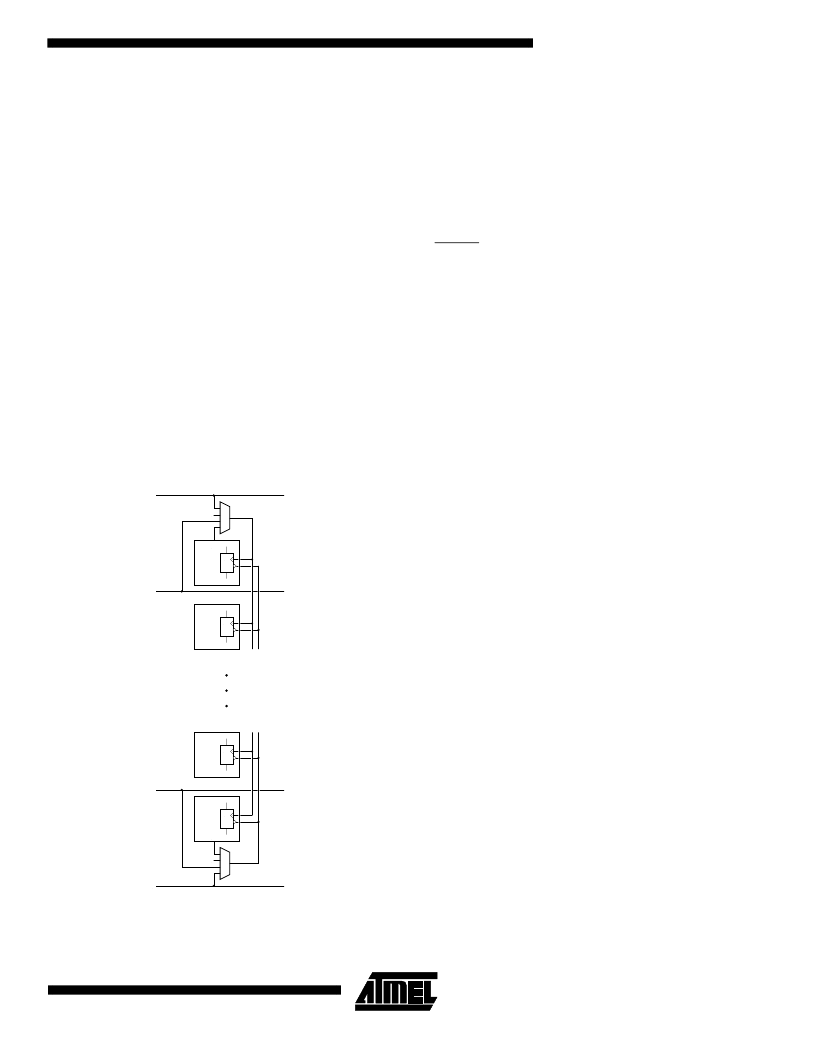

Along the top edge of the array is logic for distributing clock

signals to the D flip-flop in each logic cell (Figure 10). The

distribution network is organized by column and permits

columns of cells to be independently clocked. At the head

of each column is a user-configurable multiplexer providing

the clock signal for that column. It has four inputs:

Global clock supplied through the CLOCK pin

Express bus adjacent to the distribution logic

“

A

”

output of the cell at the head of the column

Logical constant

“

1

”

to conserve power (no clock)

Through the global clock, the network provides low-skew

distribution of an externally supplied clock to any or all of

the columns of the array. The global clock pin is also con-

nected directly to the array via the A input of the upper left

and right corner cells (AW on the left, and AN on the right).

The express bus is useful in distributing a secondary clock

to multiple columns when the global clock line is used as a

primary clock. The A output of a cell is useful in providing a

clock signal to a single column. The constant

“

1

”

is used to

reduce power dissipation in columns using no registers.

Figure 10.

Column Clock and Column Reset

Asynchronous Reset

Along the bottom edge of the array is logic for asynchro-

nously resetting the D flip-flops in the logic cells

(Figure 10). Like the clock network, the asynchronous reset

network is organized by column and permits columns to be

independently reset. At the bottom of each column is a

user-configurable multiplexer providing the reset signal for

that column. It has four inputs:

Global asynchronous reset supplied through the

RESET pin

Express bus adjacent to the distribution logic

“

A

”

output of the cell at the foot of the column

Logical constant

“

1

”

to conserve power

The asynchronous reset logic uses these four inputs in the

same way that the clock distribution logic does. Through

the global asynchronous reset, any or all columns can be

reset by an externally supplied signal. The global asynchro-

nous reset pin is also connected directly to the array via the

A input of the lower left and right corner cells (AS on the

left, and AE on the right). The express bus can be used to

distribute a secondary reset to multiple columns when the

global reset line is used as a primary reset, the A output of

a cell can also provide an asynchronous reset signal to a

single column, and the constant

“

1

”

is used by columns

with registers requiring no reset. All registers are reset dur-

ing power-up.

Input/Output

The Atmel architecture provides a flexible interface

between the logic array, the configuration control logic and

the I/O pins.

Two adjacent cells

–

an

“

exit

”

and an

“

entrance

”

cell

–

on

the perimeter of the logic array are associated with each

I/O pin.

There are two types of I/Os: A-type (Figure 11) and B-type

(Figure 12). For A-type I/Os, the edge-facing A output of an

exit cell is connected to an output driver, and the edge-

facing A input of the adjacent entrance cell is connected to

an input buffer. The output of the output driver and the input

of the input buffer are connected to a common pin.

B-type I/Os are the same as A-type I/Os, but use the B

inputs and outputs of their respective entrance and exit

cells. A- and B-type I/Os alternate around the array Control

of the I/O logic is provided by user-configurable memory

bits.

A

D

Q

"1"

GLOBAL

CLOCK

EXPRESS

BUS

GLOBAL

CLOCK

EXPRESS

BUS

R

O

U

T

I

N

G

B

U

R

I

E

D

D

E

D

I

C

A

T

E

D

CELL

D

Q

CELL

A

D

Q

EXPRESS

BUS

GLOBAL

RESET

EXPRESS

BUS

GLOBAL

RESET

CELL

D

Q

CELL

"1"

相关PDF资料 |

PDF描述 |

|---|---|

| AT6005LV-4QC | Coprocessor Field Programmable Gate Arrays |

| AT6010-2JC | Coprocessor Field Programmable Gate Arrays |

| AT6010-2JI | Coprocessor Field Programmable Gate Arrays |

| AT6010-2QC | Coprocessor Field Programmable Gate Arrays |

| AT6010-2QI | Coprocessor Field Programmable Gate Arrays |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AT6005LV-4QC | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Coprocessor Field Programmable Gate Arrays |

| AT-601(40) | 功能描述:衰减器 -互连 RoHS:否 制造商:Pomona Electronics 最大衰减: 容差: 频率范围:DC to 500 MHz 阻抗:50 Ohms 功率额定值:2 W 端接类型:Crimp 连接器类型:BNC Male / Female 工作温度范围:0 C to + 102 C |

| AT60100 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:TRANSISTOR | BJT | NPN | 8MA I(C) | CHIP |

| AT6010-2JC | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Coprocessor Field Programmable Gate Arrays |

| AT6010-2JI | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Coprocessor Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。