参数资料

| 型号: | ATF1502ASV-15JI44 |

| 厂商: | Atmel |

| 文件页数: | 19/25页 |

| 文件大小: | 0K |

| 描述: | IC CPLD EE HP 15NS 44-PLCC |

| 标准包装: | 27 |

| 系列: | ATF15xx |

| 可编程类型: | 系统内可编程(最少 10,000 次编程/擦除循环) |

| 最大延迟时间 tpd(1): | 15.0ns |

| 电压电源 - 内部: | 3 V ~ 3.6 V |

| 宏单元数: | 32 |

| 输入/输出数: | 32 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-LCC(J 形引线) |

| 供应商设备封装: | 44-PLCC |

| 包装: | 管件 |

3

1615J–PLD–01/06

ATF1502ASV

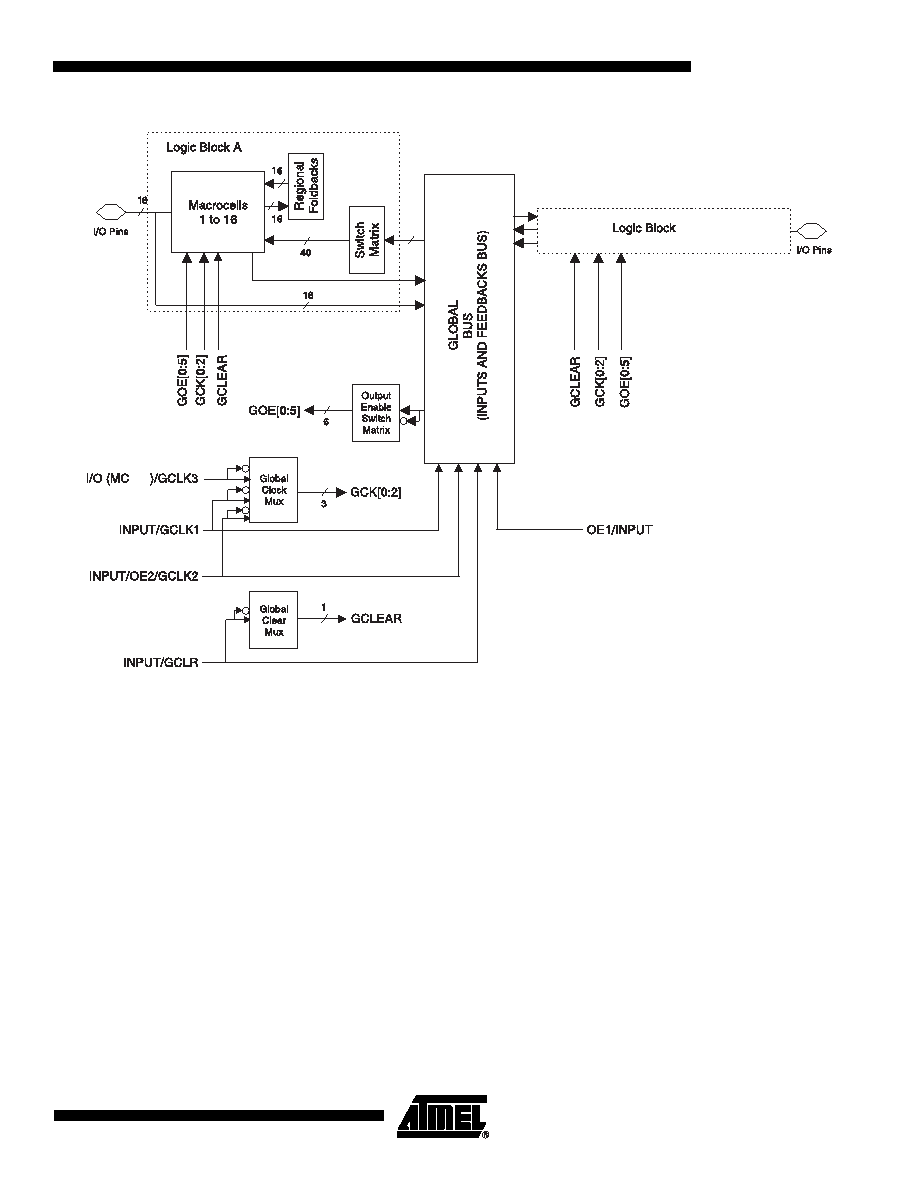

Figure 1-3.

Block Diagram

Each of the 32 macrocells generates a buried feedback that goes to the global bus. Each input

and I/O pin also feeds into the global bus. The switch matrix in each logic block then selects 40

individual signals from the global bus. Each macrocell also generates a foldback logic term that

goes to a regional bus. Cascade logic between macrocells in the ATF1502ASV allows fast, effi-

cient generation of complex logic functions. The ATF1502ASV contains four such logic chains,

each capable of creating sum term logic with a fan-in of up to 40 product terms.

The ATF1502ASV macrocell, shown in Figure 1, is flexible enough to support highly complex

logic functions operating at high speed. The macrocell consists of five sections: product terms

and product term select multiplexer, OR/XOR/CASCADE logic, a flip-flop, output select and

enable, and logic array inputs.

Unused product terms are automatically disabled by the compiler to decrease power consump-

tion. A security fuse, when programmed, protects the contents of the ATF1502ASV. Two bytes

(16 bits) of User Signature are accessible to the user for purposes such as storing project name,

part number, revision or date. The User Signature is accessible regardless of the state of the

security fuse.

The ATF1502ASV device is an in-system programmable (ISP) device. It uses the industry stan-

dard 4-pin JTAG interface (IEEE Std. 1149.1), and is fully compliant with JTAG’s Boundary-scan

Description Language (BSDL). ISP allows the device to be programmed without removing it from

B

32

相关PDF资料 |

PDF描述 |

|---|---|

| ATF1502BE-5AX44 | IC CPLD 64MC 1.8V 44-TQFP |

| ATF1504ASVL-20QI100 | IC CPLD 20NS LOWV LOWPWR 100QPFP |

| ATF1504BE-5AX100 | IC CPLD 64MC 1.8V 100-TQFP |

| ATF1508ASL-25QI160 | IC CPLD 25NS LOW PWR 160PQFP |

| ATF1508ASVL-20JU84 | IC CPLD 20NS LOWV LOW PWR 84PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ATF1502ASV-15JU44 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD 32 MACROCELL ISP STD PWR 3.3V RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| ATF1502ASV-20AC44 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD 32 MACROCELL ISP STD PWR 3.3V RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| ATF1502ASV-20AI44 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD 32 MACROCELL ISP STD PWR 3.3V RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| ATF1502ASV-20JC44 | 功能描述:CPLD - 复杂可编程逻辑器件 ASICS RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| ATF1502ASV-20JI44 | 功能描述:CPLD - 复杂可编程逻辑器件 ASICS RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。