参数资料

| 型号: | ATF16V8B-15SU |

| 厂商: | Atmel |

| 文件页数: | 14/26页 |

| 文件大小: | 0K |

| 描述: | IC PLD EE 15NS 20-SOIC |

| 标准包装: | 37 |

| 系列: | 16V8 |

| 可编程类型: | EE PLD |

| 宏单元数: | 8 |

| 输入电压: | 5V |

| 速度: | 15ns |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 20-SOIC W |

| 包装: | 管件 |

| 产品目录页面: | 610 (CN2011-ZH PDF) |

21

7707F–AVR–11/10

AT90USB82/162

4.

Write new EEPROM data to EEDR (optional).

5.

Write a logical one to the EEMPE bit while writing a zero to EEPE in EECR.

6.

Within four clock cycles after setting EEMPE, write a logical one to EEPE.

The EEPROM can not be programmed during a CPU write to the Flash memory. The software

must check that the Flash programming is completed before initiating a new EEPROM write.

Step 2 is only relevant if the software contains a Boot Loader allowing the CPU to program the

Flash. If the Flash is never being updated by the CPU, step 2 can be omitted. See “Memory Pro-

gramming” on page 243 for details about Boot programming.

Caution: An interrupt between step 5 and step 6 will make the write cycle fail, since the

EEPROM Master Write Enable will time-out. If an interrupt routine accessing the EEPROM is

interrupting another EEPROM access, the EEAR or EEDR Register will be modified, causing the

interrupted EEPROM access to fail. It is recommended to have the Global Interrupt Flag cleared

during all the steps to avoid these problems.

When the write access time has elapsed, the EEPE bit is cleared by hardware. The user soft-

ware can poll this bit and wait for a zero before writing the next byte. When EEPE has been set,

the CPU is halted for two cycles before the next instruction is executed.

Bit 0 – EERE: EEPROM Read Enable

The EEPROM Read Enable Signal EERE is the read strobe to the EEPROM. When the correct

address is set up in the EEAR Register, the EERE bit must be written to a logic one to trigger the

EEPROM read. The EEPROM read access takes one instruction, and the requested data is

available immediately. When the EEPROM is read, the CPU is halted for four cycles before the

next instruction is executed.

The user should poll the EEPE bit before starting the read operation. If a write operation is in

progress, it is neither possible to read the EEPROM, nor to change the EEAR Register.

The calibrated Oscillator is used to time the EEPROM accesses. Table 5-2 lists the typical pro-

gramming time for EEPROM access from the CPU.

The following code examples show one assembly and one C function for writing to the

EEPROM. The examples assume that interrupts are controlled (e.g. by disabling interrupts glob-

ally) so that no interrupts will occur during execution of these functions. The examples also

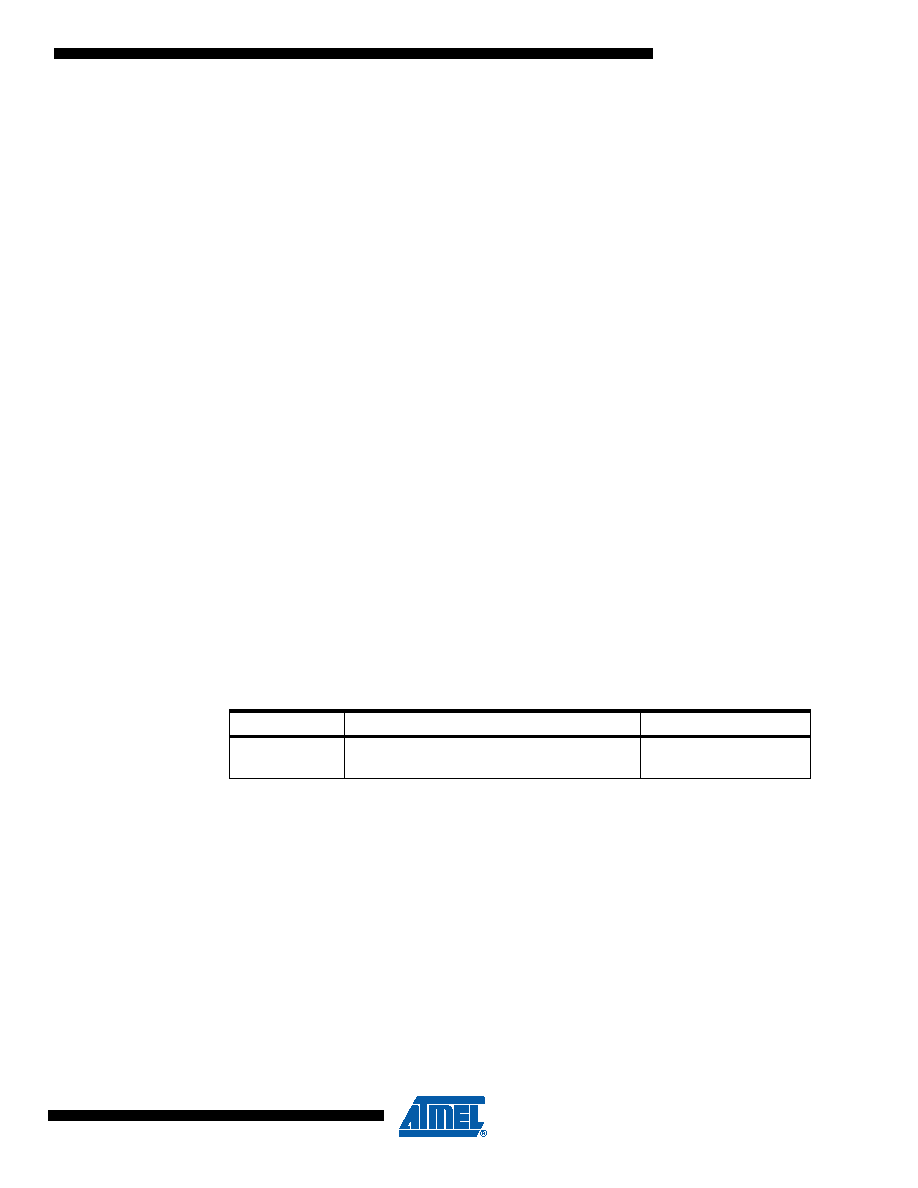

Table 5-2.

EEPROM Programming Time

Symbol

Number of Calibrated RC Oscillator Cycles

Typ Programming Time

EEPROM write

(from CPU)

26,368

3.3 ms

相关PDF资料 |

PDF描述 |

|---|---|

| IDT71342SA35PF | IC SRAM 32KBIT 35NS 64TQFP |

| 1-84984-4 | CONN FFC 14POS 1.00MM VERT PCB |

| MPC866TCVR100A | IC MPU POWERQUICC 100MHZ 357PBGA |

| 4-1734839-6 | CONN FPC 46POS .5MM RT ANG SMD |

| MPC8275VRMIBA | IC MPU POWERQUICC II 516-PBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ATF16V8B-15SU SL383 | 制造商:Atmel Corporation 功能描述:SPLD ATF16V8B Family 250 Gates 8 Macro Cells 62MHz 5V 20-Pin SOIC 制造商:Atmel Corporation 功能描述:SPLD ATF16V8B Family 250 Gates 8 Macro Cells 62MHz CMOS Technology 5V 20-Pin SOIC 制造商:Atmel 功能描述:SPLD ATF16V8B Family 250 Gates 8 Macro Cells 62MHz CMOS Technology 5V 20-Pin SOIC 制造商:Atmel 功能描述:SPLD ATF16V8B Family 250 Gates 8 Macro Cells 62MHz 5V 20-Pin SOIC |

| ATF16V8B-15XC | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Highperformance EE PLD |

| ATF16V8B-15XI | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Electrically-Erasable PLD |

| ATF16V8B-15XU | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Highperformance EE PLD |

| ATF16V8B-25GC | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Electrically-Erasable PLD |

发布紧急采购,3分钟左右您将得到回复。