- 您现在的位置:买卖IC网 > PDF目录4539 > BR24T32NUX-WTR (Rohm Semiconductor)IC EEPROM I2C 32K 400KHZ 8-VSON PDF资料下载

参数资料

| 型号: | BR24T32NUX-WTR |

| 厂商: | Rohm Semiconductor |

| 文件页数: | 7/22页 |

| 文件大小: | 0K |

| 描述: | IC EEPROM I2C 32K 400KHZ 8-VSON |

| 标准包装: | 1 |

| 格式 - 存储器: | EEPROMs - 串行 |

| 存储器类型: | EEPROM |

| 存储容量: | 32K (4K x 8) |

| 速度: | 400kHz |

| 接口: | I²C,2 线串口 |

| 电源电压: | 1.7 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-UFDFN 裸露焊盘 |

| 供应商设备封装: | VSON008X2030 |

| 包装: | 标准包装 |

| 其它名称: | BR24T32NUX-WDKR |

�� �

�

BR24T� □□□□� Series�

�Technical� Note�

�I� C� BUS� data� communication�

�I� C� BUS� data� communication� starts� by� start� condition� input,� and� ends� by� stop� condition� input.� Data� is� always� 8bit� long,�

�and� acknowledge� is� always� required� after� each� byte.� I� C� BUS� carries� out� data� transmission� with� plural� devices� connected�

�●� I� 2� C� BUS� communication�

�2�

�2�

�2�

�by� 2� communication� lines� of� serial� data� (SDA)� and� serial� clock� (SCL).�

�Among� devices,� there� are� “master”� that� generates� clock� and� control� communication� start� and� end,� and� “slave”� that� is�

�controlled� by� address� peculiar� to� devices.� EEPROM� becomes� “slave”.� And� the� device� that� outputs� data� to� bus� during�

�data� communication� is� called� “transmitter”,� and� the� device� that� receives� data� is� called� “receiver”.�

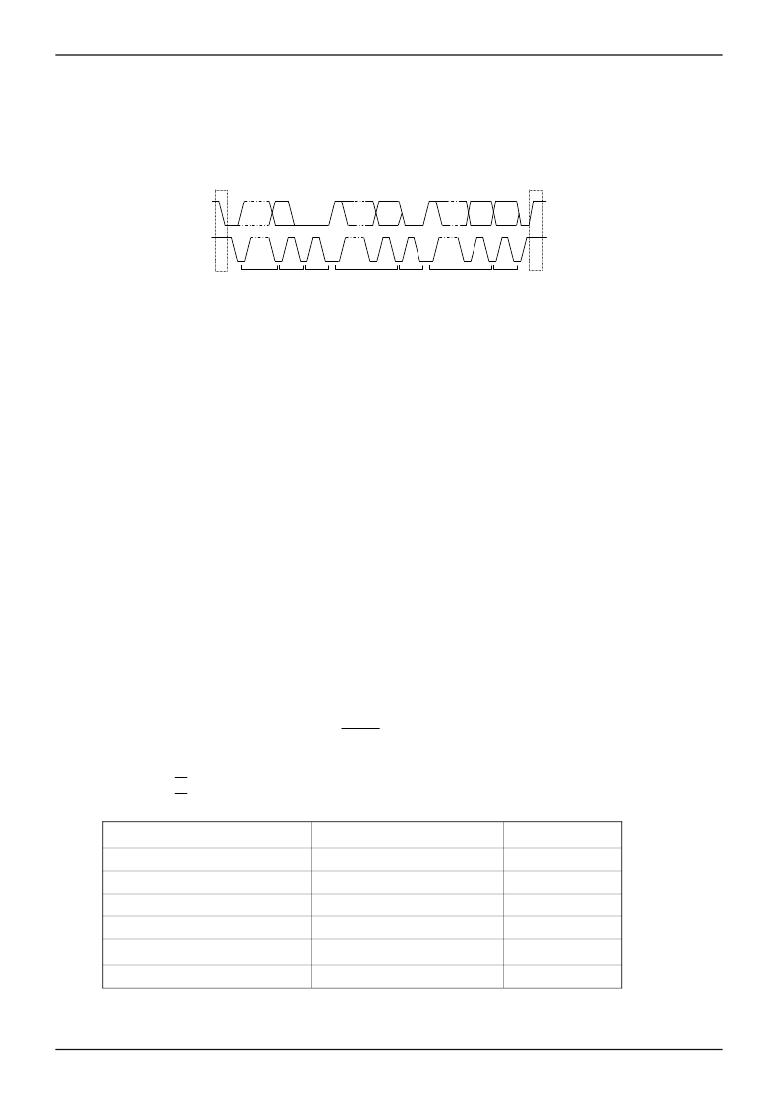

�SDA�

�SCL�

�1-7�

�8�

�9�

�1-7�

�8�

�9�

�1-7�

�8�

�9�

�S�

�P�

�START�

�ADDRESS�

�R/W�

�ACK�

�DATA�

�ACK�

�DATA�

�ACK�

�STOP�

�condition�

�condition�

�Fig.37� Data� transfer� timing�

�○� Start� condition� (Start� bit� recognition)�

�?� Before� executing� each� command,� start� condition� (start� bit)� where� SDA� goes� from� 'HIGH'� down� to� 'LOW'� when� SCL� is�

�'HIGH'� is� necessary.�

�?� This� IC� always� detects� whether� SDA� and� SCL� are� in� start� condition� (start� bit)� or� not,� therefore,� unless� this� confdition� is�

�satisfied,� any� command� is� executed.�

�○� Stop� condition� (stop� bit� recongnition)�

�?� Each� command� can� be� ended� by� SDA� rising� from� 'LOW'� to� 'HIGH'� when� stop� condition� (stop� bit),� namely,� SCL� is� 'HIGH'�

�○� Acknowledge� (ACK)� signal�

�?� This� acknowledge� (ACK)� signal� is� a� software� rule� to� show� whether� data� transfer� has� been� made� normally� or� not.� In�

�master� and� slave,� the� device� (μ-COM� at� slave� address� input� of� write� command,� read� command,� and� this� IC� at� data�

�output� of� read� command)� at� the� transmitter� (sending)� side� releases� the� bus� after� output� of� 8bit� data.�

�?� The� device� (this� IC� at� slave� address� input� of� write� command,� read� command,� and� μ-COM� at� data� output� of� read�

�command)� at� the� receiver� (receiving)� side� sets� SDA� 'LOW'� during� 9� clock� cycles,� and� outputs� acknowledge� signal� (ACK�

�signal)� showing� that� it� has� received� the� 8bit� data.�

�?� This� IC,� after� recognizing� start� condition� and� slave� address� (8bit),� outputs� acknowledge� signal� (ACK� signal)� 'LOW'.�

�?� Each� write� action� outputs� acknowledge� signal� (ACK� signal)� 'LOW',� at� receiving� 8bit� data� (word� address� and� write� data).�

�?� Each� read� action� outputs� 8bit� data� (read� data),� and� detects� acknowledge� signal� (ACK� signal)� 'LOW'.� When�

�acknowledge� signal� (ACK� signal)� is� detected,� and� stop� condition� is� not� sent� from� the� master� (μ-COM)� side,� this� IC�

�continues� data� output.� When� acknowledge� signal� (ACK� signal)� is� not� detected,� this� IC� stops� data� transfer,� and�

�recognizes� stop� cindition� (stop� bit),� and� ends� read� action.� And� this� IC� gets� in� status.�

�○� Device� addressing�

�?� Output� slave� address� after� start� condition� from� master.�

�?� The� significant� 4� bits� of� slave� address� are� used� for� recognizing� a� device� type.�

�The� device� code� of� this� IC� is� fixed� to� '1010'.�

�?� Next� slave� addresses� (A2� A1� A0� ---� device� address)� are� for� selecting� devices,� and� plural� ones� can� be� used� on� a� same�

�bus� according� to� the� number� of� device� addresses.�

�?� The� most� insignificant� bit� (R/W� ---� READ� /� WRITE� )� of� slave� address� is� used� for� designating� write� or� read� action,�

�and� is� as� shown� below.�

�Setting� R� /� W� to� 0� -------� write� (setting� 0� to� word� address� setting� of� random� read)�

�Setting� R� /� W� to� 1� -------� read�

�Type�

�Slave� address�

�Maximum� number� of�

�Connected� buses�

�BR24T01-W,BR24T02-W�

�1�

�0�

�1� 0�

�A2� A1�

�――�

�A0� R/� W�

�8�

�BR24T04-W�

�BR24T08-W�

�BR24T16-W�

�1�

�1�

�1�

�0�

�0�

�0�

�1�

�1�

�1�

�0�

�0�

�0�

�A2�

�A2�

�P2�

�A1�

�P1�

�P1�

�P0�

�P0�

�P0�

�――�

�R/� W�

�――�

�R/� W�

�――�

�R/� W�

�4�

�2�

�1�

�BR24T32-W,BR24T64-W,BR24T128-W,�

�BR24T256-W,BR24T512-W�

�BR24T1M-W�

�1�

�1�

�0�

�0�

�1� 0�

�1� 0�

�A2�

�A2�

�A1�

�A1�

�A0�

�P0�

�――�

�R/� W�

�――�

�R/� W�

�8�

�4�

�P0� ~� P2� are� page� select� bits.�

�www.rohm.com�

�?� 2011� ROHM� Co.,� Ltd.� All� rights� reserved.�

�7/21�

�2011.03� -� Rev.A�

�相关PDF资料 |

PDF描述 |

|---|---|

| AGLN030V5-ZVQG100I | IC FPGA NANO 1KB 30K 100VQFP |

| HBC65DRYN-S93 | CONN EDGECARD 130PS DIP .100 SLD |

| AGL030V2-VQ100 | IC FPGA 1KB FLASH 30K 100-VQFP |

| HMC35DRYH-S93 | CONN EDGECARD 70POS DIP .100 SLD |

| HBC65DRYH-S93 | CONN EDGECARD 130PS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BR24T32NUX-WTR(G) | 制造商:ROHM Semiconductor 功能描述: |

| BR24T32-W | 制造商:ROHM Semiconductor 功能描述: |

| BR24T512FJWGE2 | 制造商:ROHM 制造商全称:Rohm 功能描述:High Reliability Serial EEPROMs |

| BR24T512FJWGTR | 制造商:ROHM 制造商全称:Rohm 功能描述:High Reliability Serial EEPROMs |

| BR24T512FVJFVMWGE2 | 制造商:ROHM 制造商全称:Rohm 功能描述:High Reliability Serial EEPROMs |

发布紧急采购,3分钟左右您将得到回复。