- 您现在的位置:买卖IC网 > PDF目录256292 > BU-61559D1-100S (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 PDF资料下载

参数资料

| 型号: | BU-61559D1-100S |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| 封装: | 45.70 X 53.30 MM, 5.30 MM HEIGHT, CERAMIC, DDIP-78 |

| 文件页数: | 20/32页 |

| 文件大小: | 438K |

| 代理商: | BU-61559D1-100S |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

27

Data Device Corporation

www.ddc-web.com

BU-61559 Series

E-03/06-0

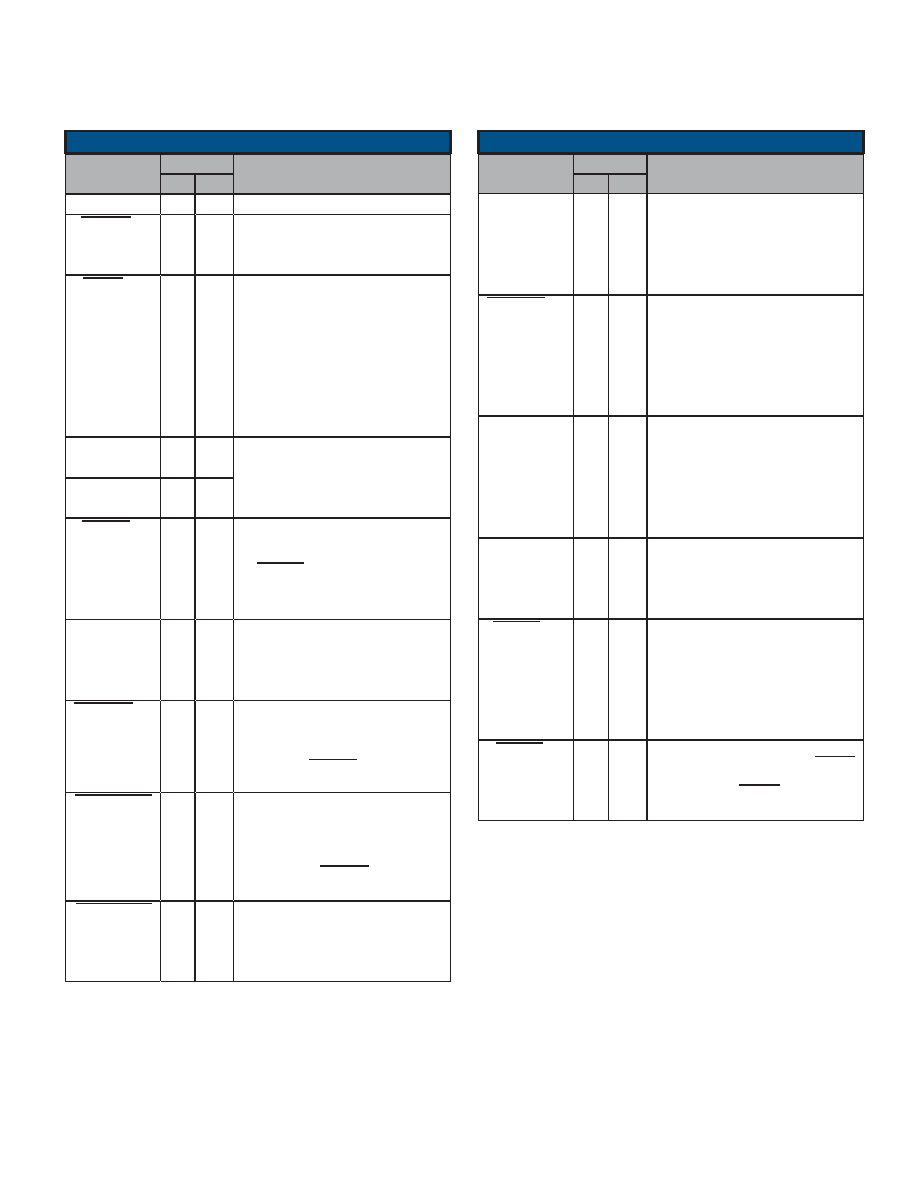

16 MHz clock input.

CLOCK IN (I)

32

56

Master Clear. Negative true Reset

input, normally asserted low following

power turn-on.

MSTCLR (I)

71

55

In Command. In BC mode, asserted

low throughout processing cycle for

each message. In RT mode, asserted

low following receipt of Command Word

and kept low until completion of current

message sequence. In Monitor mode,

goes low following MONITOR START

command, kept low while monitor is on-

line, goes high following RESET com-

mand.

INCMD (O)

70

57

The 1553 Channel A and/or Channel B

transmitters may be inhibited by assert-

ing the respective TX_INH input(s) high.

*

TX_INH_A (I)

76

45

TX_INH_B (I)

57

34

If this input is asserted low the

Subsystem Flag bit will be set in the

BU-61559's RT Status Word. A low on

the SSFLAG input overrides a logic “1”

of the respective bit (bit 8) of

Configuration Register #1.

SSFLAG (I)

37

46

In BC or RT modes, this output will be

asserted as a low level following a word

or format error and remain low until the

start of the next message.

MSG_ERR (O)

12

23

In RT/transparent mode, this output will

pulse low for nominally 62.5 ns (signal

is one clock cycle wide) and occurs in

the middle of the transfer cycle, coinci-

dent with the MEMWR pulse for writing

the command word to RAM.

CMD_STR (O)

13

25

In RT/transparent mode, this output will

pulse low for nominally 62.5 ns (signal

is one clock cycle wide) and occurs

during the third of four clock cycles dur-

ing a data word write cycle, in the same

time frame that MEMWR writes the

received data word to RAM.

RX_DTA_STR

(O)

52

24

In RT/transparent mode, this output will

pulse low for nominally 62.5 nsec (sig-

nal is one clock cycle wide) and occurs

during the third of four clock cycles dur-

ing a data word read cycle.

TX_DTA_STR

(O)

53

26

SIGNAL NAME

PIN NO.

DESCRIPTION

DIP

FLAT

MISCELLANEOUS (16)

Broadcast Enable. If connected to logic

1, the BU-61559 will recognize RT

Address 31 as the broadcast address. If

connected to logic 0, RT Address 31

may be used as a discrete RT address.

BRO_ENA (I)

54

28

Broadcast Command received is an

active low signal that occurs 1.35 to

2.25 s following the mid-parity bit

crossing of a received broadcast com-

mand word that remains low until

receipt of a subsequent command word

to the BU-61559’s own RT address.

BCSTRCV (O)

16

31

Illegalization Enable. If connected to

logic 1, designates shared RAM

addresses 0300-03FF to be dedicated

for command illegalization in RT mode.

If set to logic 0, illegalization is disabled

and addresses 0300-03FF may be

used for stack or message data. Has no

effect in BC or MT modes.

ILLENA (I)

17

33

External Time Tag Clock input. For

BC/RT modes. Use may be designated

by means of Configuration Register # 2.

If not used, should be connected to

+5V or ground.

TAG_CLK (I)

15

29

In RT mode, is updated following every

valid, nonbroadcast message. Will be

asserted low if the RT fails its loopback

test (invalid or mismatch to last trans-

mitted word) or if a 768 s timeout con-

dition occurs. Cleared by reset or as a

result of next valid, non-broadcast mes-

sage.

RT_FAIL (O)

55

30

Active low input used to control RT

FLAG bit in RT Status Word. If RTFAIL

is low, the RT FLAG bit will be set. May

be connected to RTFAIL.

RTFLAG (I)

56

32

SIGNAL NAME

PIN NO.

DESCRIPTION

DIP

FLAT

MISCELLANEOUS (16) (CONT)

* The operation of the TX_INH_A/B inputs also effects the operation of the BC off-

line self test. If the inhibit is high when an off-line BC self test is run, a “loop test”

failure will occur.

TABLE 7. SIGNAL DESCRIPTIONS BY FUNCTIONAL GROUPS (CONT)

相关PDF资料 |

PDF描述 |

|---|---|

| BU-61559D1-100W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D1-430W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D1-430 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D2-420Z | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D2-430Z | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU-61580 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553 Components |ACE |

| BU-61580G1-100 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580G1-110 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580G1-120 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580G1-200 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

发布紧急采购,3分钟左右您将得到回复。