- 您现在的位置:买卖IC网 > PDF目录256144 > BU-61580S3-110K (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 PDF资料下载

参数资料

| 型号: | BU-61580S3-110K |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| 封装: | 48.30 X 25.40 MM, 4.19 MM HEIGHT, DIP-70 |

| 文件页数: | 32/44页 |

| 文件大小: | 563K |

| 代理商: | BU-61580S3-110K |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

38

Data Device Corporation

www.ddc-web.com

BU-65170/61580/61585

H1 web-09/02-0

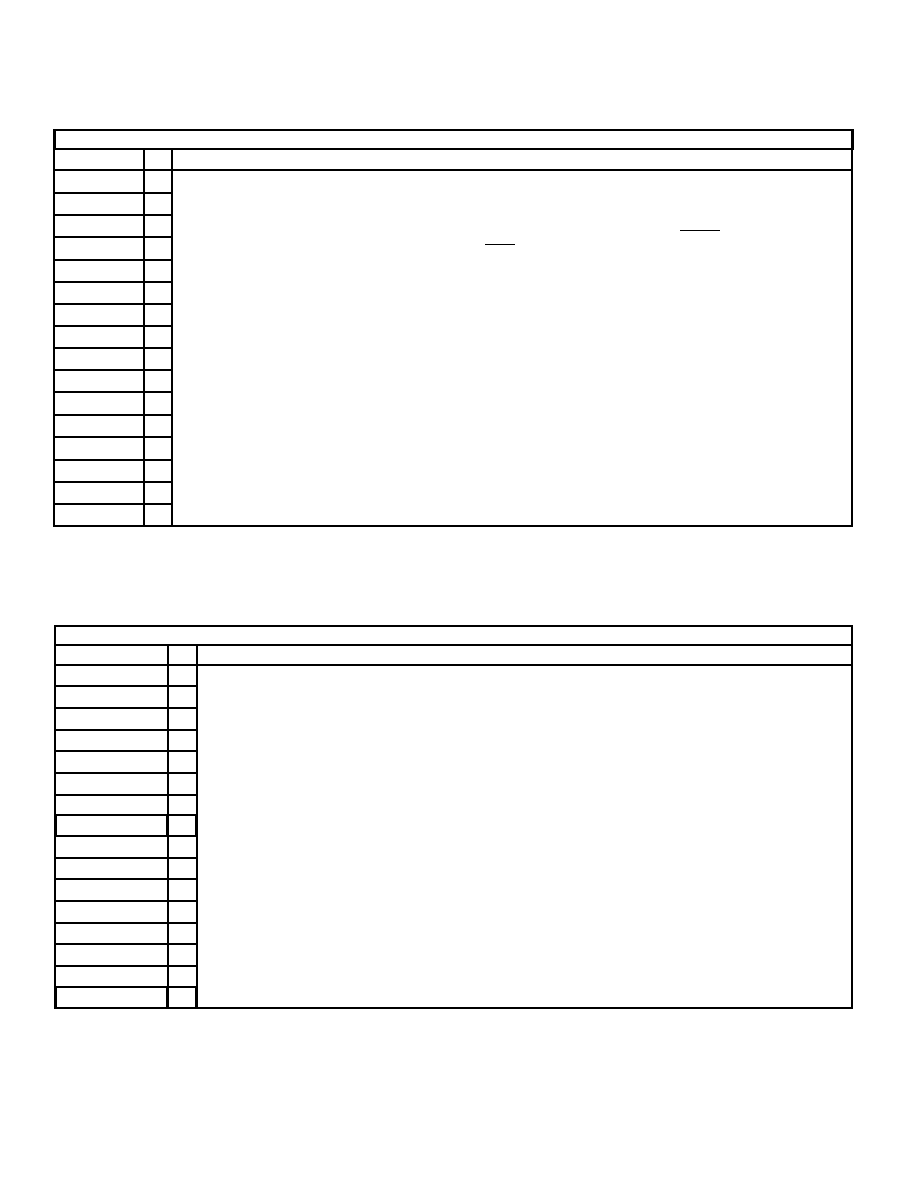

TABLE 33. SIGNAL DESCRIPTIONS FOR BU-65170/61571, BU-61580/61585, BU-61586

(G, S or V PACKAGE) (CONTINUED)

ADDRESS BUS (16)

A04

A10

21

13

16-bit bidirectional address bus. In both the buffered and transparent modes, the host CPU accesses the BU-65170/61580

registers and 4K words of internal RAM by A11 through A0 (BU-61585 uses A13 through A0). The host CPU performs register

selection by A4 through A0.In the buffered mode, A15-A0 are inputs only. In the transparent mode, A15-A0 are inputs during

CPU accesses and drive outward (towards the CPU) when the 1553 protocol/memory management logic accesses up to 64K

x 16 of external RAM. The address bus drives outward only in the transparent when the signal DTACK is low (indicating that

the 61580 has control of the processor interface bus) and IOEN is high (indicating that this is not a CPU access). Most of the

time, including immediately after power turn-on RESET, the A15-A0 outputs will be in their disabled (high impedance) state.

25

20

12

A00

A05

A11

24

17

11

A01

A06

A12

23

16

10

A02

A07

A13

22

15

9

A03

A08

A14

14

8

A09

A15 (MSB)

DESCRIPTION

16-bit bidirectional data bus. This bus interfaces the host processor to the internal registers and 4K words of RAM(12K of

RAM for the BU-61585). In addition, in the transparent mode, this bus allows data transfers to take place between the

internal protocol/memory management logic and up to 64K x 16 of external RAM. Most of the time, the outputs for D15

through D0 are in their high impedance state. They drive outward in the buffered or transparent mode when the host CPU

reads the internal RAM or registers. Or, in the transparent mode, when the protocol/memory management logic is

accessing (either reading or writing) internal RAM or writing to external RAM.

46

D10

D00

47

D01

48

D02

49

D03

D04

50

51

D05

52

D06

53

D07

55

D08

56

57

D09

58

D11

59

D12

60

D13

61

D14

62

D15 (MSB)

DATA BUS (16)

DESCRIPTION

PIN

SIGNAL NAME

SIGNAL NAME PIN

相关PDF资料 |

PDF描述 |

|---|---|

| BU-61580S3-442 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61580S3-480W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61580S3-820 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61580S6-420S | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61580S6-420 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU-61580S3-112 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580S3-122 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580S6-100 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580S6-110 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580S6-120 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

发布紧急采购,3分钟左右您将得到回复。