- 您现在的位置:买卖IC网 > PDF目录166540 > BU-61580S3-120L (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 PDF资料下载

参数资料

| 型号: | BU-61580S3-120L |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| 封装: | 48.30 X 25.40 MM, 4.19 MM HEIGHT, DIP-70 |

| 文件页数: | 1/44页 |

| 文件大小: | 563K |

| 代理商: | BU-61580S3-120L |

当前第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

BU-65170/61580 and BU-61585

DESCRIPTION

DDC's BU-65170, BU-61580 and

BU-61585 Bus Controller / Remote

Terminal

/

Monitor

Terminal

(BC/RT/MT)

A d v anced

Communication Engine (ACE) termi-

nals comprise a complete integrated

interface between a host processor

and a MIL-STD-1553 A and B or

STANAG 3838 bus.

The ACE series is packaged in a 1.9 -

square-inch,

70-pin,

low-profile,

cofired

MultiChip

Module

(MCM)

ceramic package that is well suited for

applications with stringent height

requirements.

The BU-61585 ACE integrates dual

transceiver, protocol, memory man-

agement, processor interface logic,

and a total of 12K words of RAM in a

choice of DIP or flat pack packages.

The BU-61585 requires +5 V power

and either -15 V or -12 V power.

The BU-61585 internal RAM can be

configured as 12K x 16 or 8K x 17.

The 8K x 17 RAM feature provides

capability for memory integrity check-

ing by implementing RAM parity gen-

eration and verification on all access-

es. To minimize board space and

“glue” logic, the ACE provides ultimate

flexibility in interfacing to a host

processor and internal/external RAM.

The advanced functional architecture

of the ACE terminals provides soft-

ware

compatibility

to

DDC's

Advanced Integrated Multiplexer (AIM)

series hybrids, while incorporating a

multiplicity of architectural enhance-

ments. It allows flexible operation

while off-loading the host processor,

ensuring data sample consistency,

and supports bulk data transfers.

The ACE hybrids may be operated at

either 12 or 16 MHz. Wire bond

options allow for programmable RT

address (hardwired is standard) and

external transmitter inhibit inputs.

MIL-STD-1553A/B NOTICE 2 RT and BC/RT/MT,

ADVANCED COMMUNICATION ENGINE (ACE)

FEATURES

Fully Integrated MIL-STD-1553

Interface Terminal

Flexible Processor/Memory

Interface

Standard 4K x 16 RAM and

Optional 12K x 16 or 8K x 17 RAM

Available

Optional RAM Parity

Generation/Checking

Automatic BC Retries

Programmable BC Gap Times

BC Frame Auto-Repeat

Flexible RT Data Buffering

Programmable Illegalization

Selective Message Monitor

Simultaneous RT/Monitor Mode

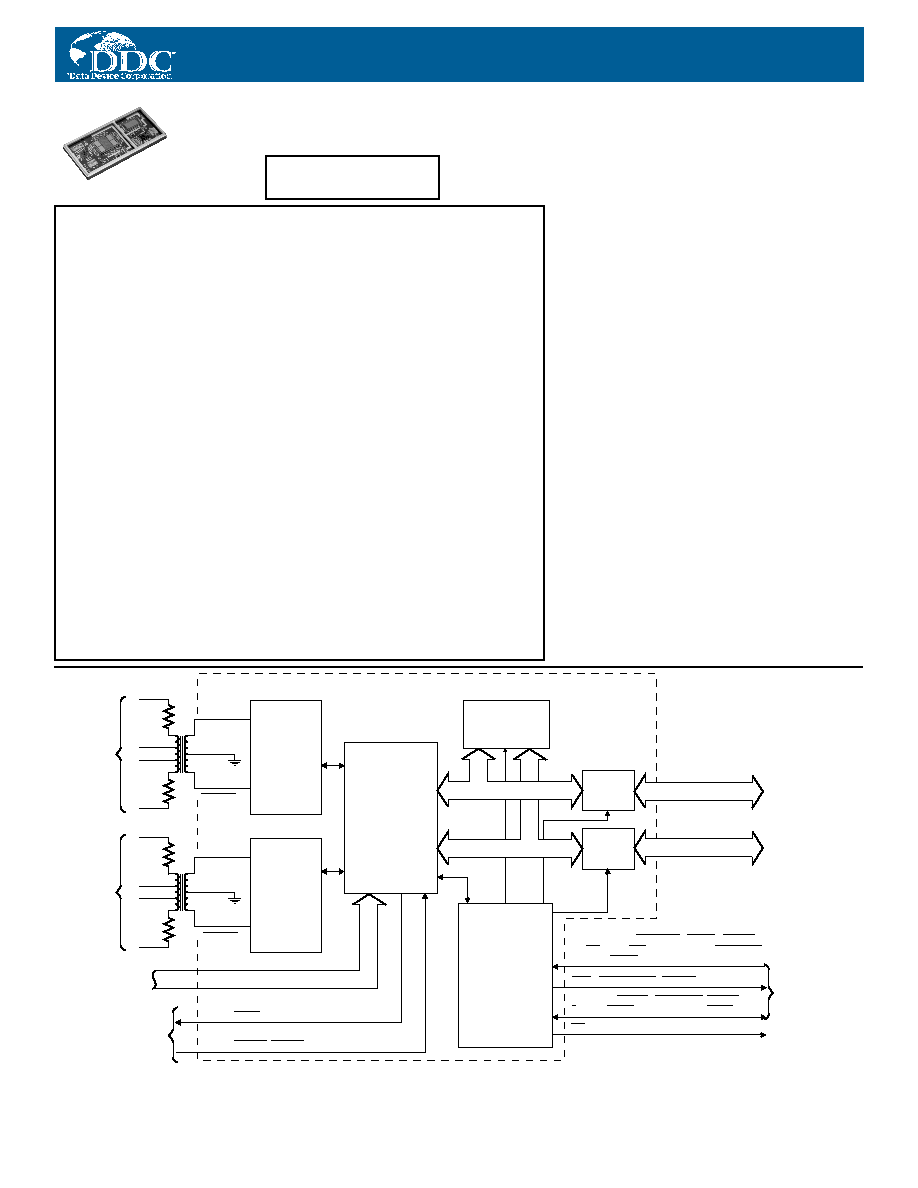

TRANSCEIVER

A

CH. A

TRANSCEIVER

B

CH. B

DUAL

ENCODER/DECODER,

MULTIPROTOCOL

AND

MEMORY

MANAGEMENT

RT ADDRESS

SHARED

RAM

ADDRESS BUS

PROCESSOR

AND

MEMORY

INTERFACE

LOGIC

DATA BUS

D15-D0

A15-A0

DATA

BUFFERS

ADDRESS

BUFFERS

PROCESSOR

DATA BUS

PROCESSOR

ADDRESS BUS

MISCELLANEOUS

INCMD

CLK_IN, TAG_CLK,

MSTCLR,SSFLAG/EXT_TRG

RTAD4-RTAD0, RTADP

TRANSPARENT/BUFFERED, STRBD, SELECT,

RD/WR, MEM/REG, TRIGGER_SEL/MEMENA-IN,

MSB/LSB/DTGRT

IOEN, MEMENA-OUT, READYD

ADDR_LAT/MEMOE, ZERO_WAIT/MEMWR,

8/16-BIT/DTREQ, POLARITY_SEL/DTACK

INT

PROCESSOR

AND

MEMORY

CONTROL

INTERRUPT

REQUEST

TX/RX_A

TX/RX_B

*

* SEE ORDERING INFORMATION FOR AVAILABLE MEMORY

1992, 1999 Data Device Corporation

ACE User’s Guide

Also Available

FIGURE 1. ACE BLOCK DIAGRAM

相关PDF资料 |

PDF描述 |

|---|---|

| BU-61580S3-140Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61580S3-170Y | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61580S3-402W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61580S3-432Y | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61580S3-440L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU-61580S3-122 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580S6-100 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580S6-110 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580S6-120 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580S6-200 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

发布紧急采购,3分钟左右您将得到回复。