- 您现在的位置:买卖IC网 > PDF目录166540 > BU-61580S3-120L (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 PDF资料下载

参数资料

| 型号: | BU-61580S3-120L |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| 封装: | 48.30 X 25.40 MM, 4.19 MM HEIGHT, DIP-70 |

| 文件页数: | 20/44页 |

| 文件大小: | 563K |

| 代理商: | BU-61580S3-120L |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

27

Data Device Corporation

www.ddc-web.com

BU-65170/61580/61585

H1 web-09/02-0

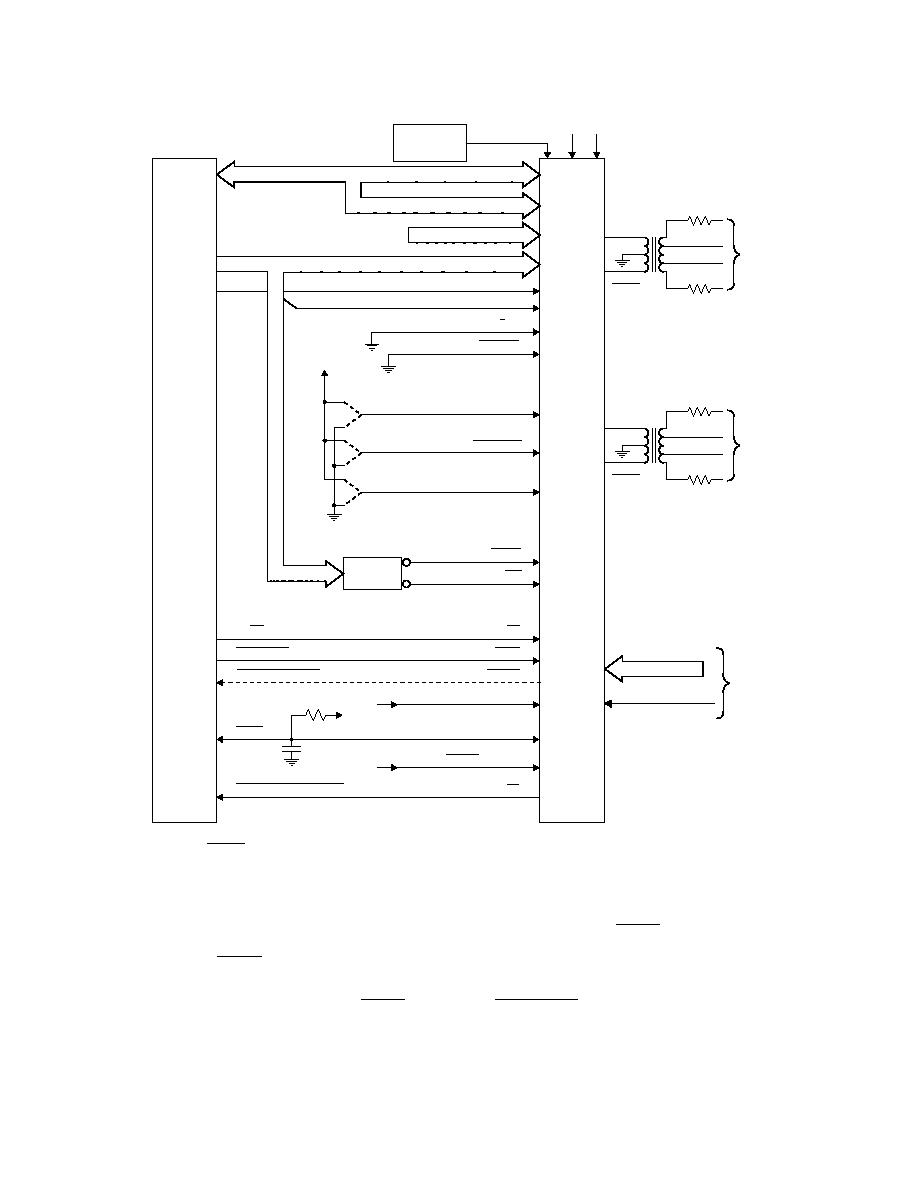

FIGURE 14. 8-BIT BUFFERED MODE

* Additional address lines A12 and A13 are required with the BU-61585.

HOST

ACE

55

55

8

7

5

4

1

2

3

CH. A

TX/RXA

55

55

8

7

5

4

1

2

3

CH. B

TX/RXB

RTAD4-RTAD0

RT

ADDRESS,

PARITY

RTADP

D15-D8

+5V

+15V

CLK IN

16 MHz

CLOCK

OSCILLATOR

POLARITY_SEL

(NOTE 3)

ZERO_WAIT

(NOTE 4)

ADDRESS

DECODER

SELECT

MEM/REG

RD/WR

STRBD

READYD

TAG_CLK

RD/WR

CPU STROBE

CPU ACKNOWLEDGE

(NOTE 6)

RESET

NOTES:

+5V

MSTCLR

SSFLAG/EXT_TRIG

INT

CPU INTERRUPT REQUEST

TRANSFERS ARE TRIGGERED BY THE MOST SIGNIFICANT

BYTE TRANSFER READ ACCESSES AND BY THE

LEAST SIGNIFICANT BYTE TRANSFER FOR WRITE ACCESSES.

IF TRIGGER_SEL = "0", THEN INTERNAL 16-BIT

TRANSFERS ARE TRIGGERED BY THE LEAST SIGNIFICANT

BYTE TRANSFER FOR READ ACESSES AND BY THE MOST

SIGNIFICANT BYTE TRANSFER FOR WRITE ACCESSES.

FOR ZERO WAIT INTERFACE (ZERO WAIT = "0"):

IF TRIGGER_SEL = "1", THEN INTERNAL 16-BIT

TRANSFERS ARE TRIGGERED BY THE LEAST SIGNIFICANT

BYTE TRANSFER, FOR BOTH READ AND WRITE ACCESSES.

IF TRIGGER_SEL = "0", THEN INTERNAL 16-BIT

TRANSFERS ARE TRIGGERED BY THE MOST SIGNIFICANT

BYTE TRANSFER, FOR BOTH READ AND WRITE ACCESSES.

6. CPU ACKNOWLEDGE PROCESSOR INPUT ONLY FOR NON-ZERO

WAIT TYPE OF INTERFACE.

1. CPU D7-D0 CONNECTS TO BOTH D15-D8 AND

D7-D0.

2. CPU ADDRESS LATCH SIGNAL PROVIDED BY PROCESSORS

WITH MULTIPLEXED ADDRESS/DATA BUFFERS.

3. IF POLARITY_SEL = "1", THEN MSB/LSB SELECTS THE MOST

SIGNIFICANT BYTE WHEN LOW, AND THE LEAST

SIGNIFICANT BYTE WHEN HIGH.

IF POLARITY_SEL = "0", THEN MSB/LSB SELECTS THE LEAST

SIGNIFICANT BYTE WHEN LOW, AND THE MOST

SIGNIFICANT BYTE WHEN HIGH.

4. ZERO WAIT SHOULD BE STRAPPED TO LOGIC "1" FOR

NON-ZERO WAIT INTERFACE AND TO LOGIC "0" FOR

ZERO WAIT INTERFACE.

5. OPERATION OF TRIGGER_SELECT INPUT IS AS FOLLOWS:

FOR NON-ZERO WAIT INTERFACE (ZERO WAIT = "1"):

IF TRIGGER_SEL = "1", THEN INTERNAL 16-BIT

A15-A12

A11-A0

N/C

ADDR_LAT

CPU ADDRESS LATCH

(NOTE 1)

16/8_BIT

TRANSPARENT/BUFFERED

+5V

CPU D7-D0

(NOTE 2)

A12-A1

CPU A12-A0

MSB/LSB

CPU A0

TRIGGER_SEL

(NOTE 5)

D7-D0

相关PDF资料 |

PDF描述 |

|---|---|

| BU-61580S3-140Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61580S3-170Y | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61580S3-402W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61580S3-432Y | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61580S3-440L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU-61580S3-122 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580S6-100 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580S6-110 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580S6-120 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580S6-200 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

发布紧急采购,3分钟左右您将得到回复。