- 您现在的位置:买卖IC网 > PDF目录166545 > BU-61580S3-120W (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 PDF资料下载

参数资料

| 型号: | BU-61580S3-120W |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| 封装: | 48.30 X 25.40 MM, 4.19 MM HEIGHT, DIP-70 |

| 文件页数: | 30/44页 |

| 文件大小: | 563K |

| 代理商: | BU-61580S3-120W |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

36

Data Device Corporation

www.ddc-web.com

BU-65170/61580/61585

H1 web-09/02-0

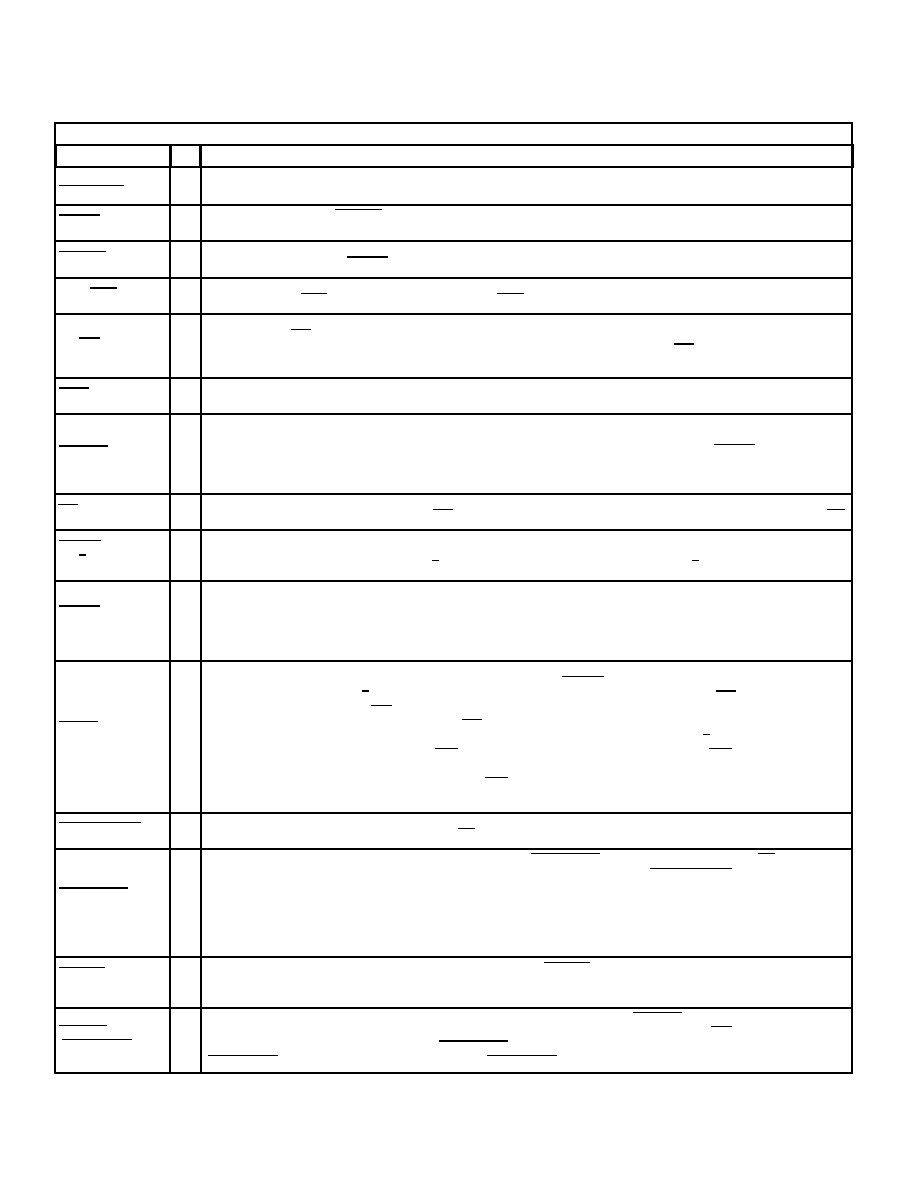

SIGNAL NAME

PROCESSOR/MEMORY INTERFACE AND CONTROL (15)

DESCRIPTION

TRANSPARENT/

BUFFERED (1)

64

STRBD (1)

4

Strobe Data. Used with SELECT to initiate and control the data transfer cycle between the host processor and the BU-

65170/61580.

SELECT (1)

3

Generally connected to a CPU address decoder output to select the BU-65170/61580 for a transfer to/from either RAM

or register. May be tied to STRBD.

MEM/REG (1)

5

Memory/Register. Generally connected to either a CPU address line or address decoder output. Selects between mem-

ory access (MEM/REG = 1 ) or register access (MEM/REG = 0 ).

6

Tri-state control for external address and data buffers. Generally not needed in the buffered mode. When low, external

buffers should be to allow the host processor access to the BU-65170/61580’s RAM and registers.

67

READYD (0)

66

INT (O)

65

Interrupt request output. If the LEVEL/PULSE interrupt bit (bit 3) of Configuration Register #2 is low, a negative pulse of

approximately 500 ns in width is output on INT. If bit 3 is high, a low level interrupt request output will be asserted on INT.

DTREQ (O)

/16/8 (I)

31

DTGRT (I)

/MSB/LSB (I)

26

32

MEMENA-OUT (O)

28

Memory Enable Output. Asserted low during both host processor and 1553 protocol/memory management memory

transfer cycles. Used as a memory chip select (CS) signal for external RAM in the transparent mode.

33

MEMOE (O)/

ADDR_LAT (I)

29

MEMWR (O)

/ZERO_WAIT (I)

30

RD/WR (1)

Used to select between the Transparent/ DMA mode (when strapped to logic 1) and the Buffered mode (when strapped

to logic 0) for the host processor interface.

IOEN (0)

Handshake output to host processor. For a nonzero wait state read access, signals that data ia available to be read on

D15 through D0. For a nonzero wait state write cycle, signals the completion of data transfer to a register or RAM loca-

tion In the buffered zero wait state mode, active high output signal (following the rising edge of STRBD ) used to indi-

cate the latching of address and data (write only) and that an internal transfer between the address/data latches and the

RAM/registers is on-going.

Data Transfer Grant or Most Significant Byte/Least Significant Byte. In transparent mode, active low input signal assert-

ed, in response to the DTREQ output, to indicate that access to the processor buses has been granted to the BU-

65170/61580. In 8-bit buffered mode, input signal used to indicate which byte is being transferred (MSB or LSB). The

POLARITY_SEL input controls the logic sense of MSB/LSB. (Note: only the 8-bit buffered mode uses MSB/LSB.) See

description of POLARITY_SEL signal. N/C in 16-bit buffered mode.

DTACK (O)/

POLARITY_SEL (I)

Data Transfer Acknowledge or Polarity Select. In transparent mode, active low output signal used to indicate acceptance

of the processor interface bus in response to a data transfer grant (DTGRT).In 16-bit buffered mode (TRANSPARENT/

BUFFERED = logic 0 and 16/8 = logic 1), input signal used to control the logic sense of the RD/WR signal. When

POLARITY_SEL is logic 1, RD/WR must be asserted high (logic 1) for a read operation and low (logic 0) for a write

operation. When POLARITY_SEL is logic 0, RD/WR must be asserted low (logic 0) for a read operation and high (logic

1) for a write operation.In 8-bit buffered mode (TRANSPARENT/BUFFERED = logic 0 and 16/8 = logic 0), input signal

used to control the logic sense of the MSB/LSB signal. When POLARITY_SEL is logic 0, MSB/LSB must be asserted

low (logic 0) to indicate the transfer of the least significant byte and high (logic 1) to indicate the transfer of the most sig-

nificant byte. When POLARITY_SEL is logic 1, MSB/LSB must be asserted high (logic 1) to indicate the transfer of the

least significant byte and low (logic 0) to indicate the transfer of the most significant byte.

MEMENA-IN (I)

/TRIGGER_SEL (I)

Memory Enable Input or Trigger Select. In transparent mode, MEMENA-IN is an active low Chip Select (CS) input to the

4K x 16 of internal shared RAM. When only using internal RAM, connect directly to MEMENA-OUT. In 8-bit buffered

mode, the input signal (TRIGGER_SEL) indicates the order of byte pairs transfer to or from the BU-65170/61580 by the

host processor. This signal has no operation (can be N/C) in the 16-bit buffered mode.In the 8-bit buffered mode, TRIG-

GER_SEL should be asserted high (logic 1) if the byte order for both read operations and write operations is MSB fol-

lowed by LSB. TRIGGER_SEL should be asserted low (logic 0) if the byte order for both read operations and write oper-

ations is LSB followed by MSB.

Memory Output Enable or Address Latch. In transparent mode, MEMOE output will be used to enable data outputs for

external RAM read cycles (normally connected to the OE signal on external RAM chips). In buffered mode, ADDR_LAT

input will be used to configure the internal address latches in latched mode (when low) or transparent mode (when high).

Memory Write or Zero Wait State. In transparent mode, active low output signal (MEMWR ) will be asserted low during

memory write transfers to strobe data into internal or external RAM (normally connected to the WR signal on external

RAM chips). In buffered mode, input signal (ZERO_WAIT) will be used to select between the zero wait mode

(ZERO_WAIT = logic 0) and the nonzero wait mode (ZERO_WAIT = logic 1).

Data Transfer Request or 16-bit/8-bit Transfer Mode Select. In transparent mode, active low output signal used to request

access to the processor interface bus (address,data, and control buses). In buffered mode, input signal used to select

between the 16-bit data transfer mode (16/8 = logic 1) and the 8 bit data transfer mode (16/8 = logic 0).

PIN

Read/Write. For host processor access, selects either reading or writing. In the 16-bit buffered mode, if polarity select is

logic ), then RD/WR is low (logic 0 ) for read accesses and high (logic 1 ) for write accesses. If polarity select is logic 1

or the configuration of the interface is a mode other than 16-bit buffered mode, then RD/WR is high (logic 1 ) for read

accesses and low (logic 0 ) for write accesses.

TABLE 33. SIGNAL DESCRIPTIONS FOR BU-65170/61571, BU-61580/61585, BU-61586

(G, S or V PACKAGE)

相关PDF资料 |

PDF描述 |

|---|---|

| BU-61580S3-410Z | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61580S3-472L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61580S3-490W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61580S3-800Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61580S3-820W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU-61580S3-122 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580S6-100 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580S6-110 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580S6-120 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

| BU-61580S6-200 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553/ARINC Bus Controller/RTU |

发布紧急采购,3分钟左右您将得到回复。