- 您现在的位置:买卖IC网 > PDF目录210363 > BU-61840B3-102L (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA128 PDF资料下载

参数资料

| 型号: | BU-61840B3-102L |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA128 |

| 封装: | 0.815 X 0.815 INCH, 0.140 INCH HEIGHT, BGA-128 |

| 文件页数: | 29/60页 |

| 文件大小: | 763K |

| 代理商: | BU-61840B3-102L |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

35

Data Device Corporation

www.ddc-web.com

BU-6174X/6184X/6186X

D-03/02-250

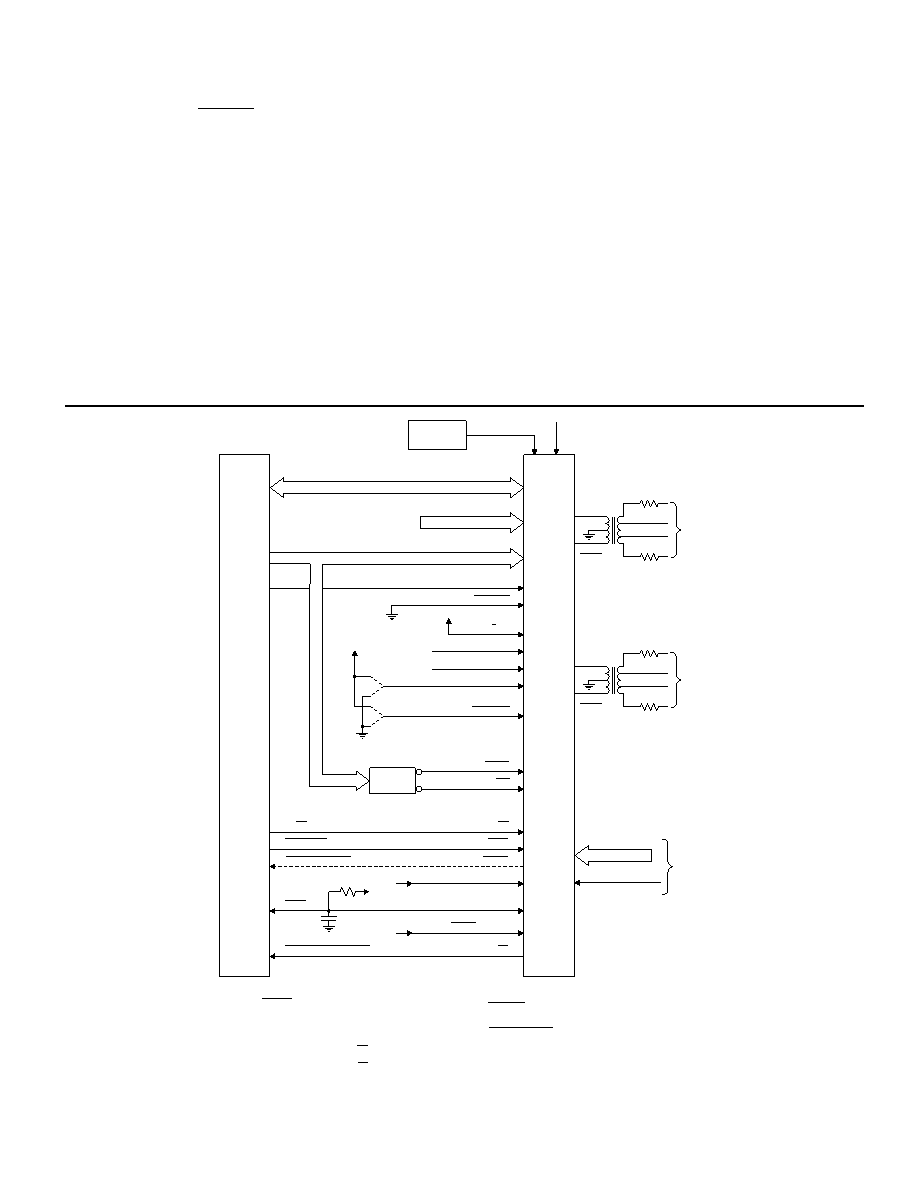

HOST

Enhanced

55

55

CH. A

TX/RXA

55

55

CH. B

TX/RXB

RTAD4-RTAD0

RT

ADDRESS,

PARITY

RTADP

D15-D0

+5V (3.3V)

(NOTE 5)

CLK IN

CLOCK

OSCILLATOR

N/C

POLARITY_SEL

(NOTE 2)

ZERO_WAIT

(NOTE 3)

ADDRESS

DECODER

SELECT

MEM/REG

RD/WR

STRBD

READYD

TAG_CLK

RD/WR

CPU STROBE

CPU ACKNOWLEDGE

(NOTE 4)

RESET

+5V

MSTCLR

SSFLAG/EXT_TRIG

INT

CPU INTERRUPT REQUEST

NOTES:

3. ZERO_WAIT SHOULD BE STRAPPED TO

LOGIC "1" FOR NON-ZERO WAIT INTERFACE

AND TO LOGIC "0" FOR ZERO WAIT INTERFACE.

4. CPU ACKNOWLEDGE PROCESSOR INPUT ONLY

FOR NON-ZERO WAIT TYPE OF INTERFACE.

5. +3.3V POWER FOR BU-61743 / 61843 / 61864 ONLY

1. CPU ADDRESS LATCH SIGNAL PROVIDED BY

PROCESSORS WITH MULTIPLEXED ADDRESS/DATA

BUSES. FOR PROCESSORS WITH NON-MULTIPLEXED

ADDRESS AND DATA BUSSES, ADDR_LAT SHOULD BE

CONNECTED TO +5V.

2. IF POLARITY_SEL = "1", RD/WR IS HIGH TO READ,

LOW TO WRITE.

IF POLARITY_SEL = "0", RD/WR IS LOW TO READ,

HIGH TO WRITE.

A15-A12

A11-A0

N/C

ADDR_LAT

TRANSPARENT/BUFFERED

CPU ADDRESS LATCH (NOTE 1)

+5V

16/8_BIT

TRIGGER_SEL

MSB/LSB

+5V

Mini-ACE

FIGURE 12. HOST PROCESSOR INTERFACE - 16-BIT BUFFERED CONFIGURATION

The Enhanced Mini-ACE's maximum host holdoff time (time prior

to the assertion of the READYD handshake signal) has been sig-

nificantly reduced. For ACE/Mini-ACE, this maximum holdoff

time is 17 internal word transfer cycles, resulting in an overall

holdoff time of approximately 4.6 s, using a 16 MHz clock. By

comparison, using the Enhanced Mini-ACE's ENHANCED CPU

ACCESS feature, this worst-case holdoff time is reduced signifi-

cantly, to a single internal transfer cycle. For example, when

operating the Enhanced Mini-ACE in its 16-bit buffered, non-zero

wait configuration with a 16 MHz clock input, this results in a

maximum overall host transfer cycle time of 632 ns for a read

cycle, or 570 ns for a write cycle.

In

addition,

for

using

the

ACE

or

Mini-ACE

in

the

transparent/DMA configuration, the maximum request-to-grant

time, which occurs prior to an RT start-of-message sequence, is

4.0 s with a 16 MHz clock, or 3.5 s with a 12 MHz clock. For

the Enhanced Mini-ACE functioning as a MIL-STD-1553B RT,

this time has been increased to 8.5 s at 10 MHz, 10 s at 16

MHz, 9 s at 12 MHz, and 10.5 s at 20MHz. This provides

greater flexibility, particularly for systems in which a host has to

arbitrate among multiple DMA requestors.

By far, the most commonly used processor interface configura-

tion is the 16-bit buffered, non-zero wait mode. This configuration

may be used to interface between 16-bit or 32-bit microproces-

sors and an Enhanced Mini-ACE. In this mode, only the

Enhanced Mini-ACE's internal 4K or 64K words of internal RAM

are used for storing 1553 message data and associated "house-

keeping" functions. That is, in this configuration, the Enhanced

Mini-ACE will never attempt to access memory on the host bus.

FIGURE 12 illustrates a generic connection diagram between a 16-

bit (or 32-bit) microprocessor and an Enhanced Mini-ACE for the 16-

bit buffered configuration, while FIGURES 13 and 14, and associat-

ed tables illustrate the processor read and write timing respectively.

相关PDF资料 |

PDF描述 |

|---|---|

| BU-61840B3-200L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA128 |

| BU-61840B3-400Y | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA128 |

| BU-61840B3-500Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA128 |

| BU-61840B3-502W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA128 |

| BU-61840B4-500Z | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA128 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU-61840B3NEW | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553 Components |μ-ACE (Micro-ACE?) |

| BU-61843 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MIL-STD-1553 Components |Enhanced Mini-ACE? |

| BU-61843F3-100 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

| BU-61843F3-110 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

| BU-61843F4-100 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

发布紧急采购,3分钟左右您将得到回复。