- 您现在的位置:买卖IC网 > PDF目录15165 > CAT1021ZI-42-GT3 (ON Semiconductor)IC SUPERVISOR CPU 2K EEPR 8MSOP PDF资料下载

参数资料

| 型号: | CAT1021ZI-42-GT3 |

| 厂商: | ON Semiconductor |

| 文件页数: | 5/20页 |

| 文件大小: | 0K |

| 描述: | IC SUPERVISOR CPU 2K EEPR 8MSOP |

| 标准包装: | 3,000 |

| 类型: | 简单复位/加电复位 |

| 监视电压数目: | 1 |

| 输出: | 开路漏极或开路集电极 |

| 复位: | 高有效/低有效 |

| 复位超时: | 最小为 130 ms |

| 电压 - 阀值: | 4.25V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-TSSOP,8-MSOP(0.118",3.00mm 宽) |

| 供应商设备封装: | 8-MSOP |

| 包装: | 带卷 (TR) |

�� �

�

CAT1021,� CAT1022,� CAT1023�

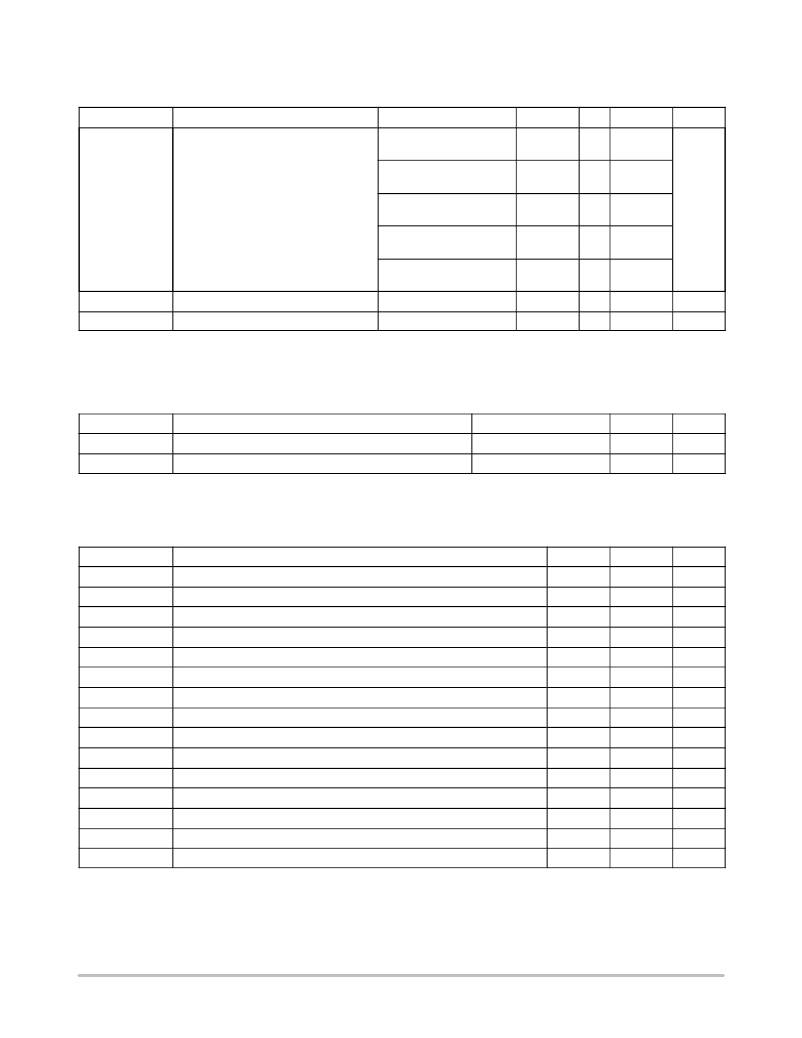

�Table� 6.� D.C.� OPERATING� CHARACTERISTICS�

�V� CC� =� 2.7� V� to� 5.5� V� and� over� the� recommended� temperature� conditions� unless� otherwise� specified.�

�Symbol�

�V� TH�

�Parameter�

�Reset� Threshold�

�Test� Conditions�

�CAT102x� ?� 45�

�(V� CC� =� 5.0� V)�

�Min�

�4.50�

�Typ�

�Max�

�4.75�

�Units�

�V�

�CAT102x� ?� 42�

�(V� CC� =� 5.0� V)�

�CAT102x� ?� 30�

�(V� CC� =� 3.3� V)�

�CAT102x� ?� 28�

�(V� CC� =� 3.3� V)�

�CAT102x� ?� 25�

�(V� CC� =� 3.0� V)�

�4.25�

�3.00�

�2.85�

�2.55�

�4.50�

�3.15�

�3.00�

�2.70�

�V� RVALID�

�V� RT� (Note� 4)�

�Reset� Output� Valid� V� CC� Voltage�

�Reset� Threshold� Hysteresis�

�1.00�

�15�

�V�

�mV�

�3.� V� IL� min� and� V� IH� max� are� reference� values� only� and� are� not� tested.�

�4.� This� parameter� is� tested� initially� and� after� a� design� or� process� change� that� affects� the� parameter.� Not� 100%� tested.�

�Table� 7.� CAPACITANCE�

�T� A� =� 25� °� C,� f� =� 1.0� MHz,� V� CC� =� 5� V�

�Symbol�

�C� OUT� (Note� 5)�

�C� IN� (Note� 5)�

�Output� Capacitance�

�Input� Capacitance�

�Test�

�Test� Conditions�

�V� OUT� =� 0� V�

�V� IN� =� 0� V�

�Max�

�8�

�6�

�Units�

�pF�

�pF�

�Table� 8.� AC� CHARACTERISTICS�

�V� CC� =� 2.7� V� to� 5.5� V� and� over� the� recommended� temperature� conditions,� unless� otherwise� specified.�

�Memory� Read� &� Write� Cycle� (Note� 6)�

�Symbol�

�Parameter�

�Min�

�Max�

�Units�

�f� SCL�

�t� SP�

�t� LOW�

�t� HIGH�

�t� R� (Note� 5)�

�t� F� (Note� 5)�

�t� HD;� STA�

�t� SU;� STA�

�t� HD;� DAT�

�t� SU;� DAT�

�t� SU;� STO�

�t� AA�

�t� DH�

�t� BUF� (Note� 5)�

�t� WC� (Note� 7)�

�Clock� Frequency�

�Input� Filter� Spike� Suppression� (SDA,� SCL)�

�Clock� Low� Period�

�Clock� High� Period�

�SDA� and� SCL� Rise� Time�

�SDA� and� SCL� Fall� Time�

�Start� Condition� Hold� Time�

�Start� Condition� Setup� Time� (for� a� Repeated� Start)�

�Data� Input� Hold� Time�

�Data� Input� Setup� Time�

�Stop� Condition� Setup� Time�

�SCL� Low� to� Data� Out� Valid�

�Data� Out� Hold� Time�

�Time� the� Bus� must� be� Free� Before� a� New� Transmission� Can� Start�

�Write� Cycle� Time� (Byte� or� Page)�

�1.3�

�0.6�

�0.6�

�0.6�

�0�

�100�

�0.6�

�50�

�1.3�

�400�

�100�

�300�

�300�

�900�

�5�

�kHz�

�ns�

�m� s�

�m� s�

�ns�

�ns�

�m� s�

�m� s�

�ns�

�ns�

�m� s�

�ns�

�ns�

�m� s�

�ms�

�5.� This� parameter� is� characterized� initially� and� after� a� design� or� process� change� that� affects� the� parameter.� Not� 100%� tested.�

�6.� Test� Conditions� according� to� “AC� Test� Conditions”� table.�

�7.� The� write� cycle� time� is� the� time� from� a� valid� stop� condition� of� a� write� sequence� to� the� end� of� the� internal� program/erase� cycle.� During� the�

�write� cycle,� the� bus� interface� circuits� are� disabled,� SDA� is� allowed� to� remain� high� and� the� device� does� not� respond� to� its� slave� address.�

�http://onsemi.com�

�5�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6307IRZ-T | IC REG CTRLR BUCK PWM VM 48-QFN |

| VE-24H-EW-F1 | CONVERTER MOD DC/DC 52V 100W |

| ECM25DTAN-S189 | CONN EDGECARD 50POS R/A .156 SLD |

| GSC22DRTN-S13 | CONN EDGECARD 44POS .100 EXTEND |

| ECM25DTAH-S189 | CONN EDGECARD 50POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CAT1021ZI-42T2 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM, Manual Reset and Watchdog Timer |

| CAT1021ZI-42-T2 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM, Manual Reset and Watchdog Timer |

| CAT1021ZI-42T3 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM, Manual Reset and Watchdog Timer |

| CAT1021ZI-42-T3 | 功能描述:监控电路 2K bit 4.2V Ind Temp RoHS:否 制造商:STMicroelectronics 监测电压数: 监测电压: 欠电压阈值: 过电压阈值: 输出类型:Active Low, Open Drain 人工复位:Resettable 监视器:No Watchdog 电池备用开关:No Backup 上电复位延迟(典型值):10 s 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:UDFN-6 封装:Reel |

| CAT1021ZI-42TE13 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM, Manual Reset and Watchdog Timer |

发布紧急采购,3分钟左右您将得到回复。