- 您现在的位置:买卖IC网 > PDF目录15162 > CAT1026YI-45-GT3 (ON Semiconductor)IC SUPERVISOR CPU 2K EEPR 8TSSOP PDF资料下载

参数资料

| 型号: | CAT1026YI-45-GT3 |

| 厂商: | ON Semiconductor |

| 文件页数: | 9/19页 |

| 文件大小: | 0K |

| 描述: | IC SUPERVISOR CPU 2K EEPR 8TSSOP |

| 标准包装: | 3,000 |

| 类型: | 多压监控器 |

| 监视电压数目: | 2 |

| 输出: | 开路漏极或开路集电极 |

| 复位: | 高有效/低有效 |

| 复位超时: | 最小为 130 ms |

| 电压 - 阀值: | 4.5V,可调 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 8-TSSOP |

| 包装: | 带卷 (TR) |

�� �

�

CAT1026,� CAT1027�

�EMBEDDED� EEPROM� OPERATON�

�The� CAT1026� and� CAT1027� feature� a� 2� ?� kbit� embedded�

�serial� EEPROM� that� supports� the� I� 2� C� Bus� data� transmission�

�protocol.� This� Inter� ?� Integrated� Circuit� Bus� protocol� defines�

�any� device� that� sends� data� to� the� bus� to� be� a� transmitter� and�

�any� device� receiving� data� to� be� a� receiver.� The� transfer� is�

�controlled� by� the� Master� device� which� generates� the� serial�

�clock� and� all� START� and� STOP� conditions� for� bus� access.�

�Both� the� Master� device� and� Slave� device� can� operate� as�

�either� transmitter� or� receiver,� but� the� Master� device� controls�

�which� mode� is� activated.�

�I� 2� C� Bus� Protocol�

�The� features� of� the� I� 2� C� bus� protocol� are� defined� as�

�follows:�

�1.� Data� transfer� may� be� initiated� only� when� the� bus� is�

�not� busy.�

�2.� During� a� data� transfer,� the� data� line� must� remain�

�stable� whenever� the� clock� line� is� high.� Any�

�changes� in� the� data� line� while� the� clock� line� is� high�

�will� be� interpreted� as� a� START� or� STOP� condition.�

�Start� Condition�

�The� START� Condition� precedes� all� commands� to� the�

�device,� and� is� defined� as� a� HIGH� to� LOW� transition� of� SDA�

�when� SCL� is� HIGH.� The� CAT1026� and� CAT1027� monitor�

�the� SDA� and� SCL� lines� and� will� not� respond� until� this�

�condition� is� met.�

�Stop� Condition�

�A� LOW� to� HIGH� transition� of� SDA� when� SCL� is� HIGH�

�determines� the� STOP� condition.� All� operations� must� end�

�with� a� STOP� condition.�

�DEVICE� ADDRESSING�

�The� Master� begins� a� transmission� by� sending� a� START�

�condition.� The� Master� sends� the� address� of� the� particular�

�slave� device� it� is� requesting.� The� four� most� significant� bits�

�of� the� 8� ?� bit� slave� address� are� programmable� in� metal� and� the�

�default� is� 1010.�

�The� last� bit� of� the� slave� address� specifies� whether� a� Read�

�or� Write� operation� is� to� be� performed.� When� this� bit� is� set� to�

�1,� a� Read� operation� is� selected,� and� when� set� to� 0,� a� Write�

�operation� is� selected.�

�After� the� Master� sends� a� START� condition� and� the� slave�

�address� byte,� the� CAT1026� and� CAT1027� monitor� the� bus�

�and� responds� with� an� acknowledge� (on� the� SDA� line)� when�

�its� address� matches� the� transmitted� slave� address.� The�

�CAT1026� and� CAT� 1027� then� perform� a� Read� or� Write�

�operation� depending� on� the� R/W� bit.�

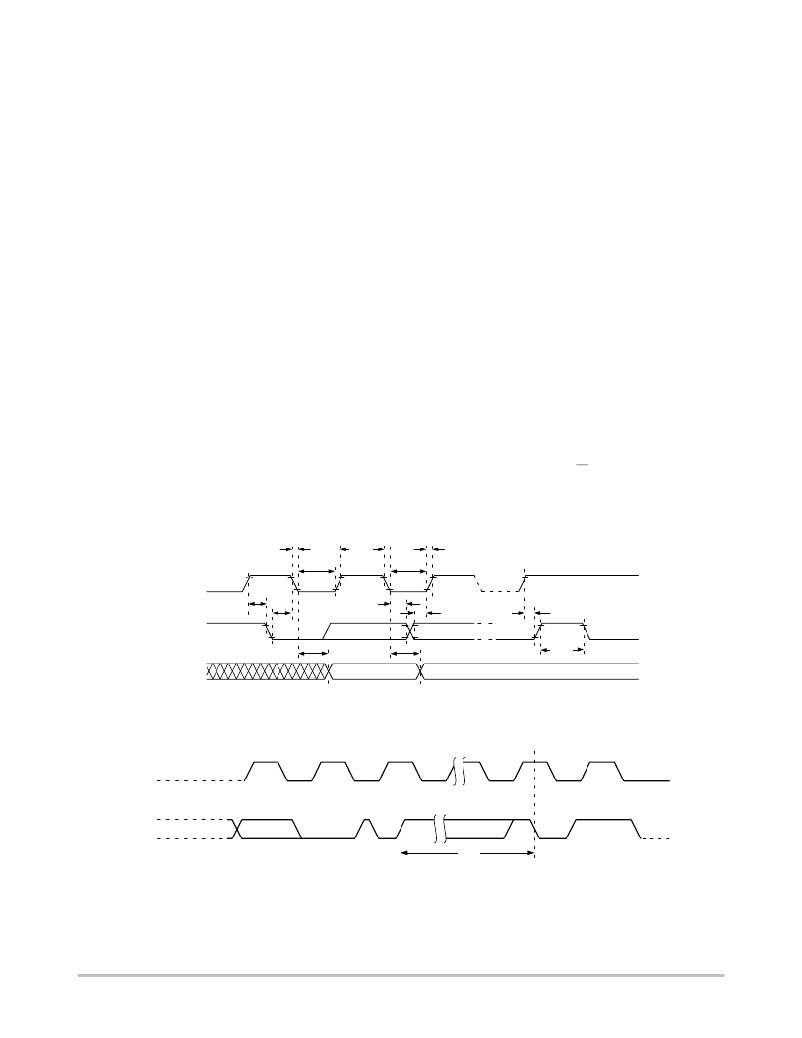

�SCL�

�tF�

�tLOW�

�tHIGH�

�tLOW�

�tR�

�tSU:STA�

�tHD:STA�

�tHD:DAT�

�tSU:DAT�

�tSU:STO�

�SDA� IN�

�tAA�

�tDH�

�tBUF�

�SDA� OUT�

�Figure� 4.� Bus� Timing�

�SCL�

�SDA�

�8TH� BIT�

�BYTE� n�

�ACK�

�tWR�

�STOP�

�CONDITION�

�Figure� 5.� Write� Cycle� Timing�

�http://onsemi.com�

�9�

�START�

�CONDITION�

�ADDRESS�

�相关PDF资料 |

PDF描述 |

|---|---|

| EEM40DTKT | CONN EDGECARD 80POS DIP .156 SLD |

| ISL6552CRZ | IC REG CTRLR BUCK PWM 20-QFN |

| ISL8120CRZ-T | IC REG CTRLR BUCK PWM VM 32-QFN |

| CAT1026YI-42-GT3 | IC SUPERVISOR CPU 2K EEPR 8TSSOP |

| ISL6401CRZ | IC REG CTRLR BST FLYBK ISO 16QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CAT1026YI-45-T3 | 制造商:ON Semiconductor 功能描述:CPU SUPERVISOR WITH 2K EEPROM - Tape and Reel |

| CAT1026YI-45TE13 | 功能描述:监控电路 2K bit 4.5V Ind Temp RoHS:否 制造商:STMicroelectronics 监测电压数: 监测电压: 欠电压阈值: 过电压阈值: 输出类型:Active Low, Open Drain 人工复位:Resettable 监视器:No Watchdog 电池备用开关:No Backup 上电复位延迟(典型值):10 s 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:UDFN-6 封装:Reel |

| CAT1026ZD4I-25T3 | 制造商:ON Semiconductor 功能描述:CPU SUPERVISOR WITH 2K EEPROM - Tape and Reel |

| CAT1026ZD4I-28T3 | 制造商:ON Semiconductor 功能描述:CPU SUPERVISOR WITH 2K EEPROM - Tape and Reel |

| CAT1026ZD4I-30T3 | 制造商:ON Semiconductor 功能描述:CPU SUPERVISOR WITH 2K EEPROM - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。