- 您现在的位置:买卖IC网 > PDF目录257723 > CAT24C043P-30 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDIP8 PDF资料下载

参数资料

| 型号: | CAT24C043P-30 |

| 元件分类: | 电源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDIP8 |

| 封装: | PLASTIC, DIP-8 |

| 文件页数: | 10/12页 |

| 文件大小: | 85K |

| 代理商: | CAT24C043P-30 |

CAT24C163/083/043/023

7

Advanced

Doc. No. 25080-00 3/98 M-1

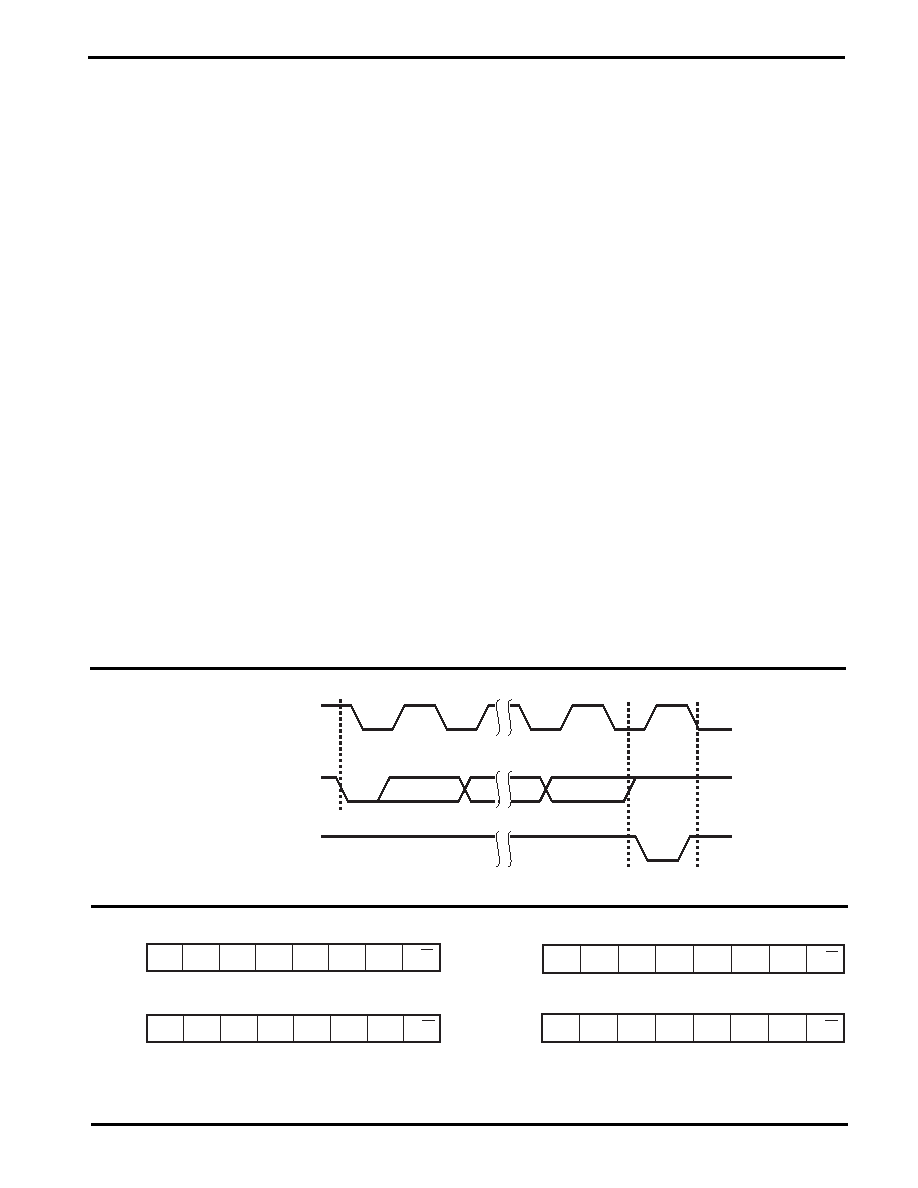

ACKNOWLEDGE

1

START

SCL FROM

MASTER

89

DATA OUTPUT

FROM TRANSMITTER

DATA OUTPUT

FROM RECEIVER

Figure 5. Acknowledge Timing

Figure 6. Slave Address Bits

FUNCTIONAL DESCRIPTION

The CAT24CXXX supports the I2C Bus data transmis-

sion protocol. This Inter-Integrated Circuit Bus protocol

defines any device that sends data to the bus to be a

transmitter and any device receiving data to be a re-

ceiver. The transfer is controlled by the Master device

which generates the serial clock and all START and

STOP conditions for bus access. The CAT24CXXX

operates as a Slave device. Both the Master device and

Slave device can operate as either transmitter or re-

ceiver, but the Master device controls which mode is

activated.

I2C BUS PROTOCOL

The features of the I2C bus protocol are defined as

follows:

(1) Data transfer may be initiated only when the bus is

not busy.

(2) During a data transfer, the data line must remain

stable whenever the clock line is high. Any changes in

the data line while the clock line is high will be interpreted

as a START or STOP condition.

START Condition

The START Condition precedes all commands to the

device, and is defined as a HIGH to LOW transition of

SDA when SCL is HIGH. The CAT24CXXX monitors the

SDA and SCL lines and will not respond until this

condition is met.

* 'X' Corresponds to Don't Care Bits (can be a zero or a one)

** a8, a9 and a10 correspond to the address of the memory array address word.

STOP Condition

A LOW to HIGH transition of SDA when SCL is HIGH

determines the STOP condition. All operations must end

with a STOP condition.

DEVICE ADDRESSING

The Master begins a transmission by sending a START

condition. The Master sends the address of the particu-

lar slave device it is requesting. The four most significant

bits of the 8-bit slave address are fixed as 1010.

The next three bits (Fig. 6) define memory addressing.

For the 24C023, the three bits are don't care. For the

24C043, the next two bits are don't care and the third bit

is the high order address bit. For the 24C083, the next

bit is don't care and the successive bits define the higher

order address bits. For the 24C163 the three bits define

higher order bits.

The last bit of the slave address specifies whether a

Read or Write operation is to be performed. When this

bit is set to 1, a Read operation is selected, and when set

to 0, a Write operation is selected.

After the Master sends a START condition and the slave

address byte, the CAT24CXXX monitors the bus and

responds with an acknowledge (on the SDA line) when

its address matches the transmitted slave address. The

CAT24CXXX then performs a Read or Write operation

depending on the state of the R/

W bit.

1

010

X

R/W

1

0

1

0

X

a8

R/W

24C023

24C043

1

010

X

a9

a8

R/W

1

0

1

0

a10

a9

a8

R/W

24C083

24C163

相关PDF资料 |

PDF描述 |

|---|---|

| CD74HC4053M96 | TRIPLE 2-CHANNEL, SGL ENDED MULTIPLEXER, PDSO16 |

| CP3020-9DGI | 3-OUTPUT 148 W DC-DC REG PWR SUPPLY MODULE |

| CAT1023LI-45-G | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDIP8 |

| CAT1023SI-45TE13 | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO8 |

| CA37NL21 | 1 ELEMENT, 7700 uH, GENERAL PURPOSE INDUCTOR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CAT24C043P-30TE13 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial CMOS E2PROM, Precision Reset Controller and Watchdog Timer |

| CAT24C043P-42TE13 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial CMOS E2PROM, Precision Reset Controller and Watchdog Timer |

| CAT24C043P-45TE13 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial CMOS E2PROM, Precision Reset Controller and Watchdog Timer |

| CAT24C043PA25TE13 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial CMOS E2PROM, Precision Reset Controller and Watchdog Timer |

| CAT24C043PA-28TE13 | 制造商:CATALYST 制造商全称:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial CMOS E2PROM, Precision Reset Controller and Watchdog Timer |

发布紧急采购,3分钟左右您将得到回复。